# **Design Example Report**

| Title                                                   | 13 W Dual Output Automotive Power Supply for<br>800V Systems Using InnoSwitch™3-AQ INN3949CQ |  |  |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|

| Specification                                           | 30 V <sub>DC</sub> – 1000 V <sub>DC</sub> Input;<br>18 V / 555 mA; 9 V / 333 mA Outputs      |  |  |  |  |  |

| Application                                             | Traction Inverter Gate and/or Emergency Power Supply                                         |  |  |  |  |  |

| <b>Author</b> Automotive Systems Engineering Department |                                                                                              |  |  |  |  |  |

| Document<br>Number                                      | DER-956Q                                                                                     |  |  |  |  |  |

| Date                                                    | July 31, 2023                                                                                |  |  |  |  |  |

| Revision                                                | 2.0                                                                                          |  |  |  |  |  |

#### **Summary and Features**

- Ultra-compact design for 800 V BEV automotive applications

- Low component count (only 62 components<sup>1</sup>) design with single 1700 V power switch

- Wide range input from 30 V<sub>DC</sub> to 1000 V<sub>DC</sub>, start-up and operation

- Reinforced 1000 V isolated transformer (IEC-60664-1 and IEC-60664-4 compliant)

- ≥80 % efficiency (450 V<sub>DC</sub> to 1000 V<sub>DC</sub>)

- Secondary-side regulated output

- Ambient operating temperature -40 °C to 105 °C

- Fully fault protected including output current limit and short-circuit protection

- Uses automotive qualified AEC-Q surface mount (SMD) components<sup>2</sup>

<sup>&</sup>lt;sup>1</sup> Excluding connectors.

<sup>&</sup>lt;sup>2</sup> AEC-Q200 transformer and input common mode choke qualification belongs to final design.

## **Table of Contents**

| _  | <b></b> |                |                                                  |     |

|----|---------|----------------|--------------------------------------------------|-----|

| 1  |         |                | uction                                           |     |

| 2  |         |                | n Specifications                                 |     |

|    | 2.1     |                | trical Specifications                            |     |

|    | 2.2     |                | ation Coordination                               |     |

|    | 2.3     |                | ironmental Specifications                        |     |

| 3  |         | Schen          | natic                                            | 9   |

| 4  |         | Circuit        | : Description                                    | 10  |

|    | 4.1     | Inp            | ut Filter                                        | 10  |

|    | 4.2     |                | n-Voltage Side Circuit                           |     |

|    | 4.3     |                | Voltage Circuit Side                             |     |

| 5  |         |                | ayout                                            |     |

| 6  |         |                | Materials                                        |     |

| 7  |         |                | former Specification                             |     |

| -  | 7.1     |                | trical Diagram                                   |     |

|    | 7.2     |                | trical Specification                             |     |

|    | 7.3     |                | nsformer Build Diagram                           |     |

|    | 7.4     |                | erial List                                       |     |

|    | 7.5     |                | ding Illustrations                               | _   |

| 8  | , .5    |                | former Design Spreadsheet                        |     |

| 9  |         |                | mance Data                                       |     |

|    | 9.1     |                | Load Input Power                                 |     |

|    | 9.2     |                | ciency                                           |     |

|    |         | .2.1           | Line Efficiency                                  |     |

|    | -       | .2.2           | Load Efficiency                                  |     |

|    | 9.3     |                | d Regulation                                     |     |

|    |         | .3.1           | 30 V <sub>DC</sub> Input                         |     |

|    |         | .3.2           | 60 V <sub>DC</sub> Input                         |     |

|    |         | .3.3           | 800 V <sub>DC</sub> Input.                       |     |

|    |         | .3.4           | 1000 V <sub>DC</sub> Input                       |     |

|    |         |                | Regulation                                       |     |

|    |         |                | Loading Condition: 18 V = Max. / 9 V = Max.      |     |

|    | ٠.      |                | Loading Condition: 18 V = Max. / 9 V = Min       |     |

|    |         | 4.3            | Loading Condition: 18 V = Min. / 9 V = Max       |     |

| 10 |         |                | nal Performance                                  |     |

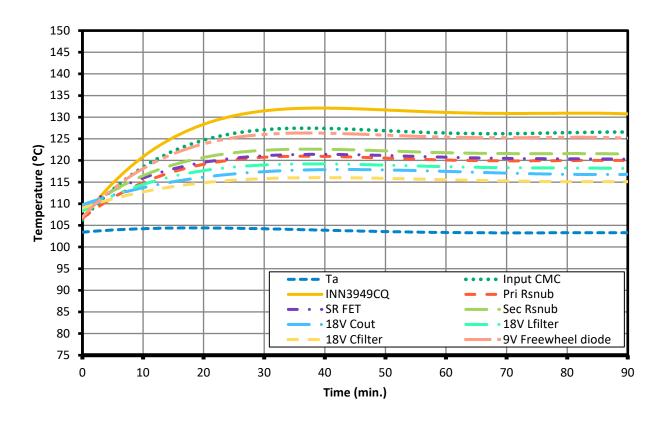

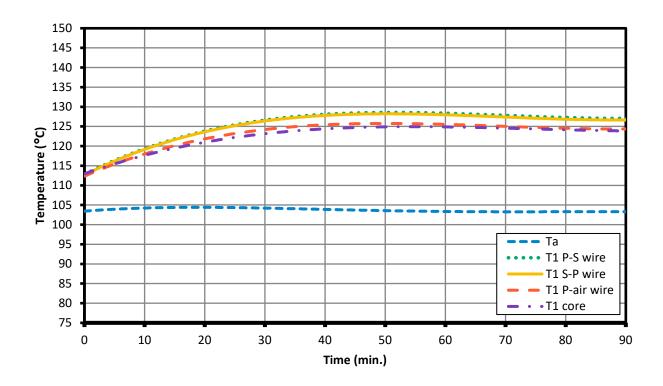

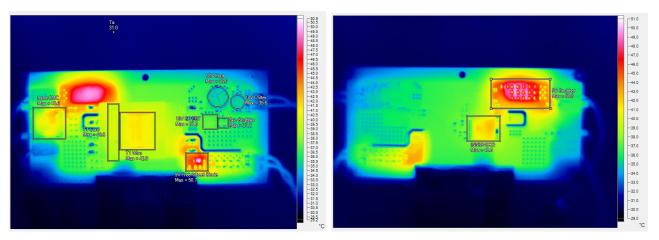

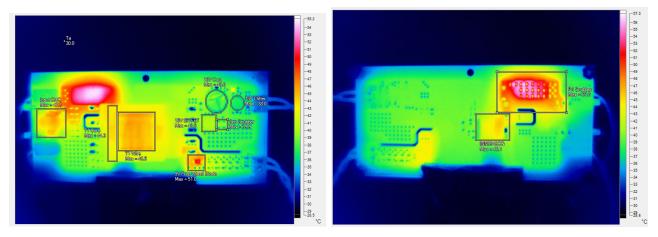

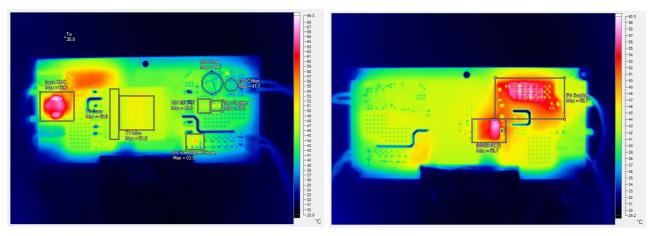

| Τ, | 10.1    | _              | rmal Data at 105 °C Ambient Temperature          |     |

|    | 10.2    |                | rmal Data at 25 °C Ambient Temperature           |     |

| 1  |         |                | forms                                            |     |

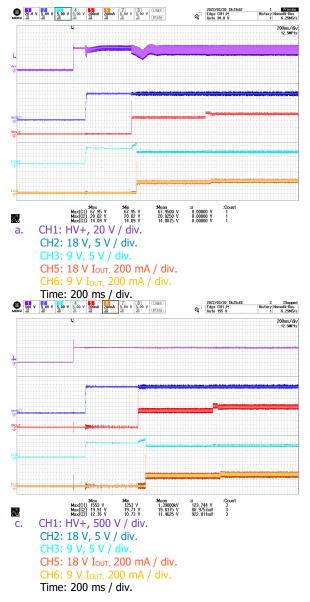

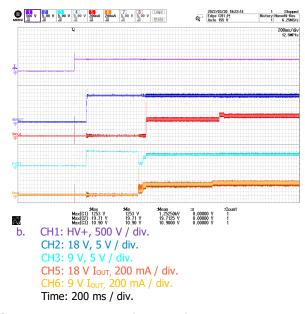

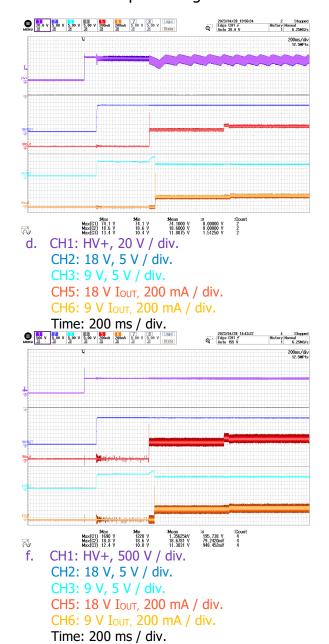

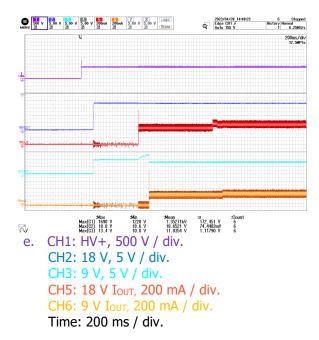

| Τ. | 11.1    | vvavci<br>Star | t-up Waveforms                                   | / ¬ |

|    |         | 1.1.1          | 25 °C Ambient Temperature                        |     |

|    |         | 1.1.2          | - 40 °C Ambient Temperature                      |     |

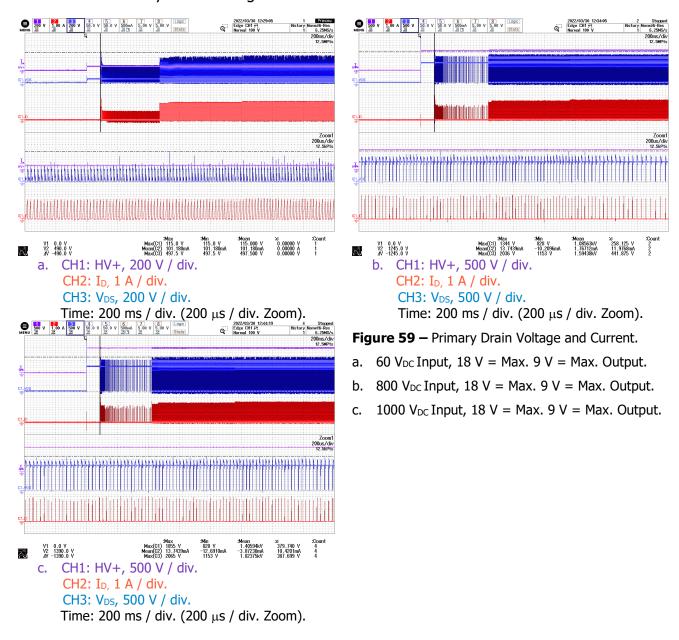

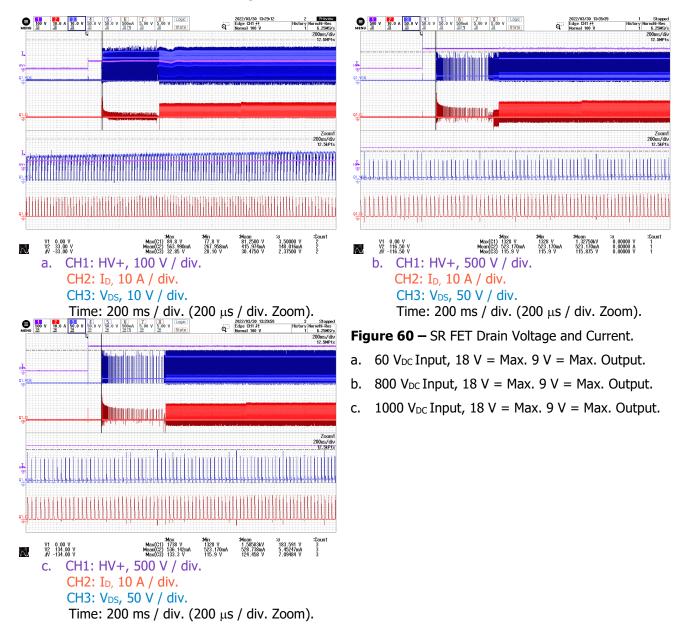

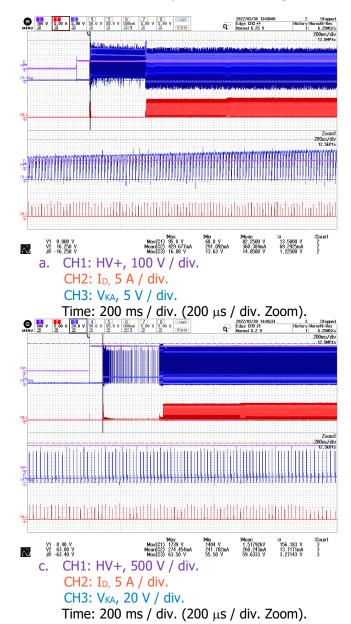

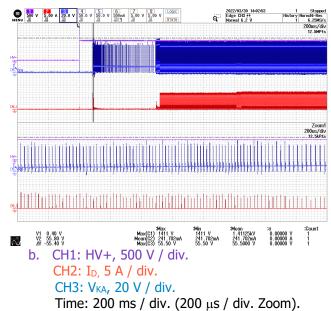

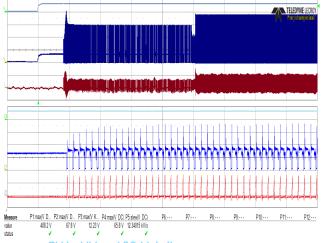

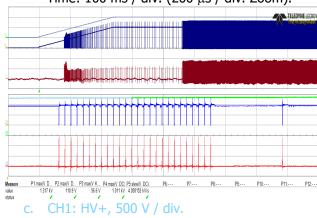

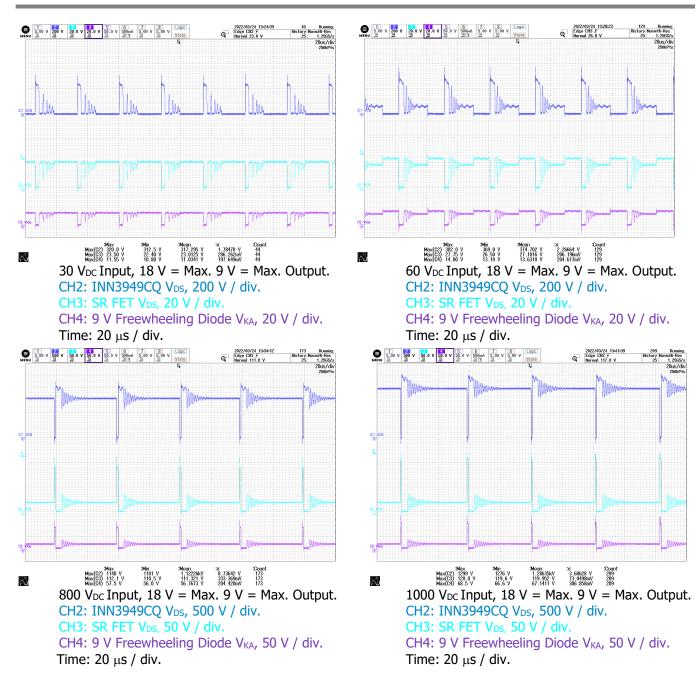

|    |         |                | ady-State Stress Waveforms                       |     |

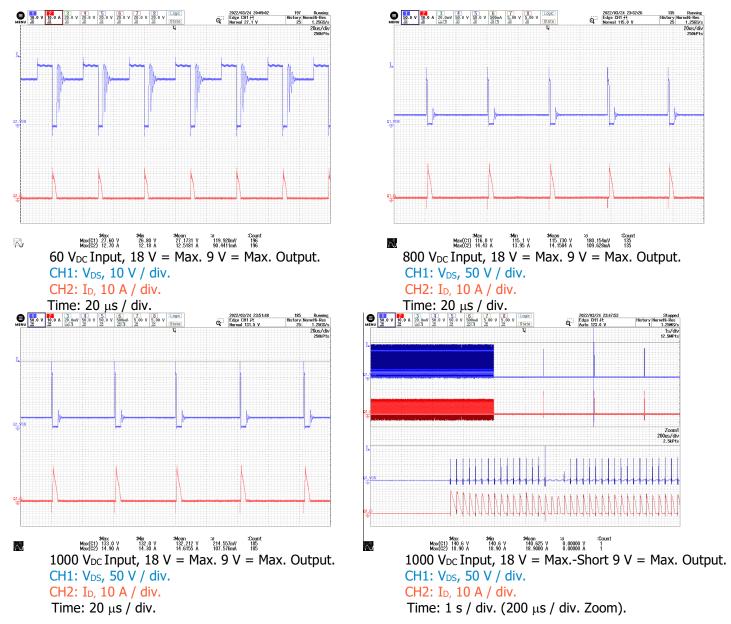

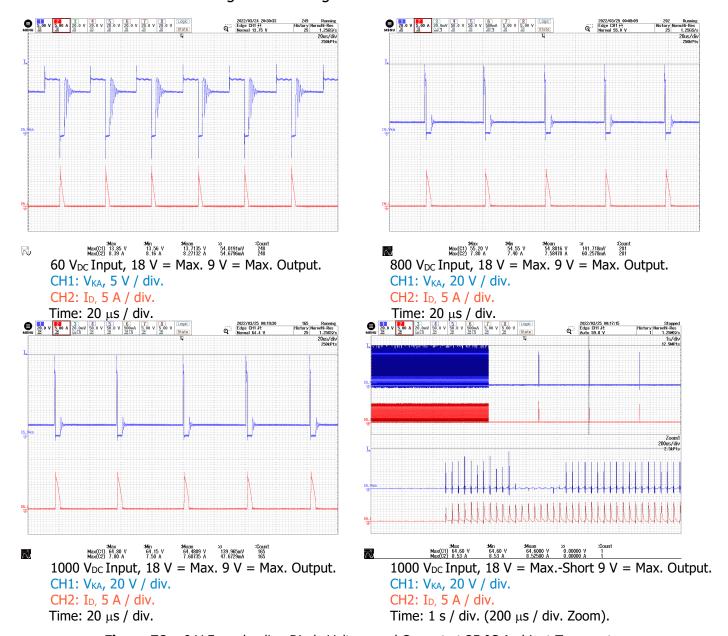

|    |         | 1.2.1          | •                                                |     |

|    |         | 1.2.1          | ·                                                |     |

|    | Ι.      | 1.4.4          | Switching waveloning at 25 C Annoted Femperature | J   |

| 11.3 Loa | nd Transient Response                                 | 88  |

|----------|-------------------------------------------------------|-----|

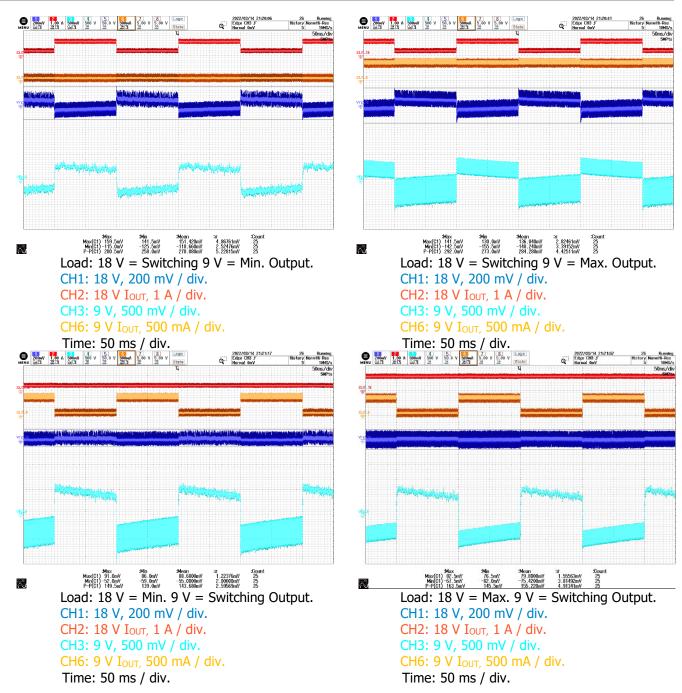

| 11.3.1   | Load Transient Response at 105 °C Ambient Temperature | 88  |

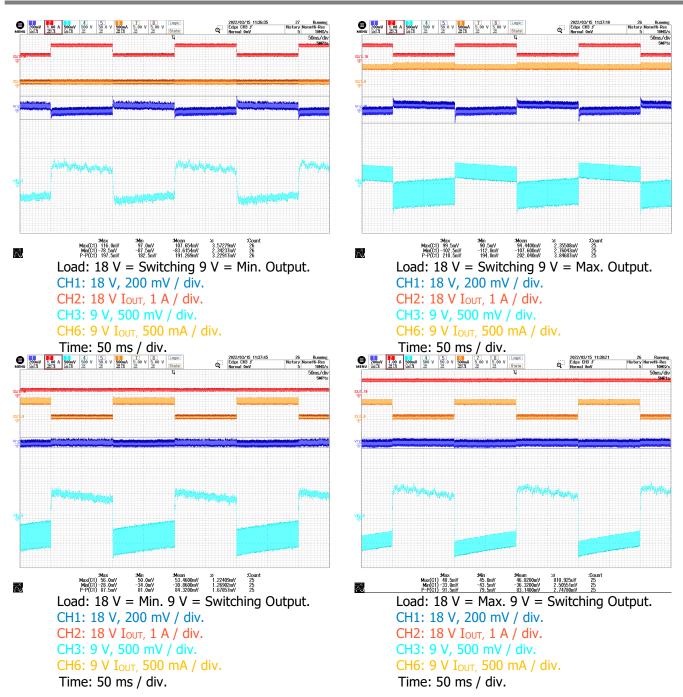

| 11.3.2   | Load Transient Response 25 °C Ambient Temperature     | 90  |

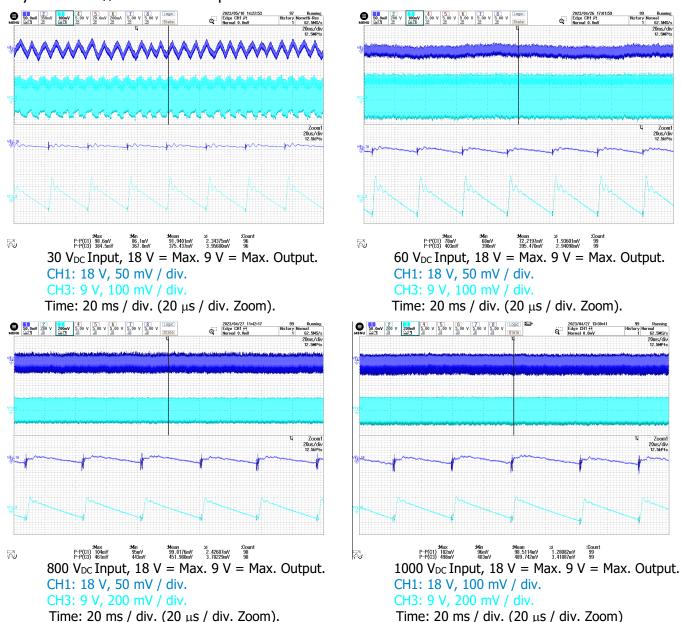

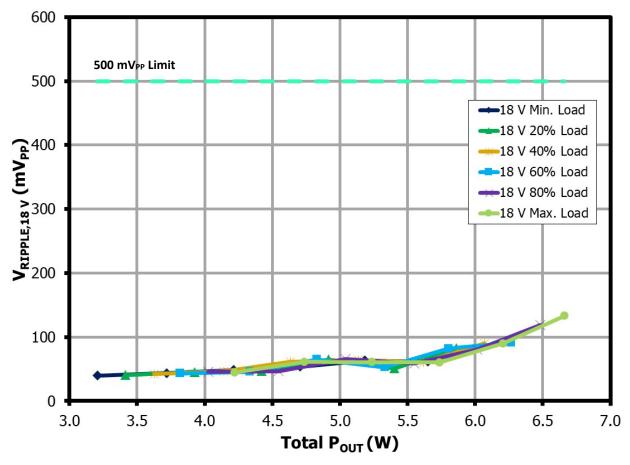

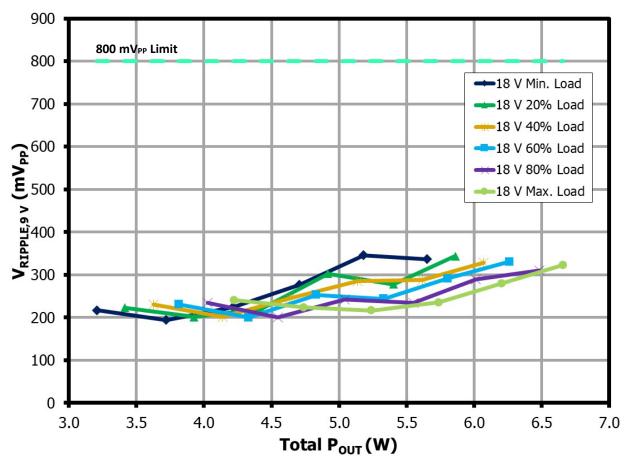

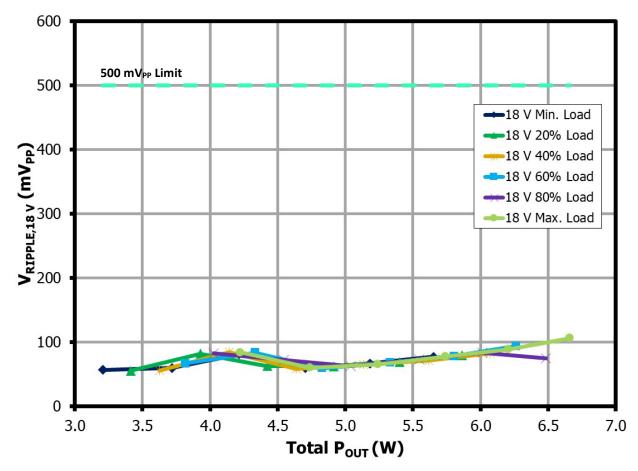

| 11.4 Out | tput Voltage Ripple Measurements                      | 92  |

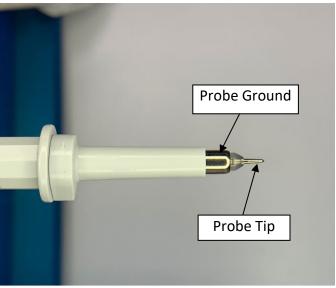

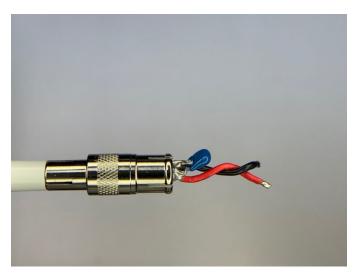

| 11.4.1   | Output Voltage Ripple Measurement Technique           | 92  |

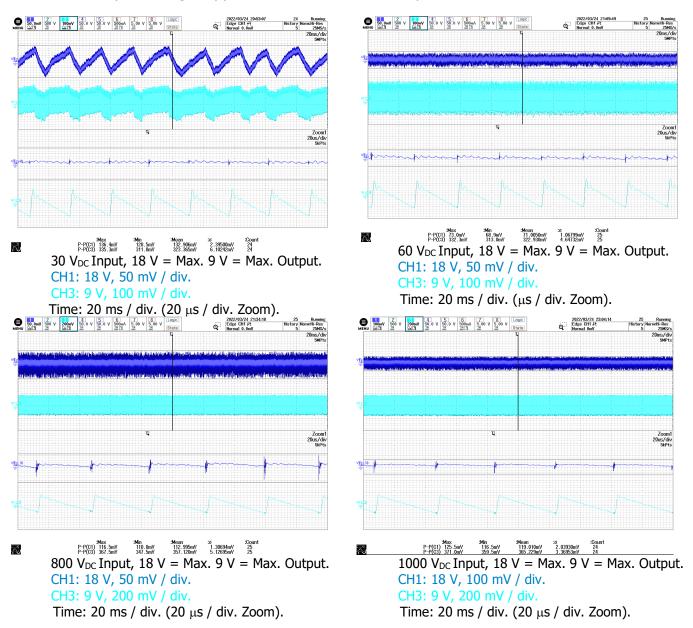

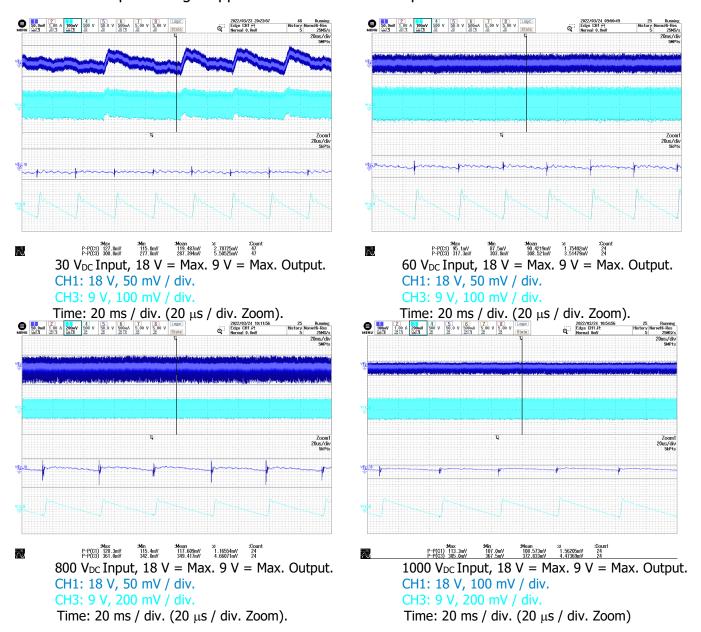

|          | Output Voltage Ripple Waveforms                       |     |

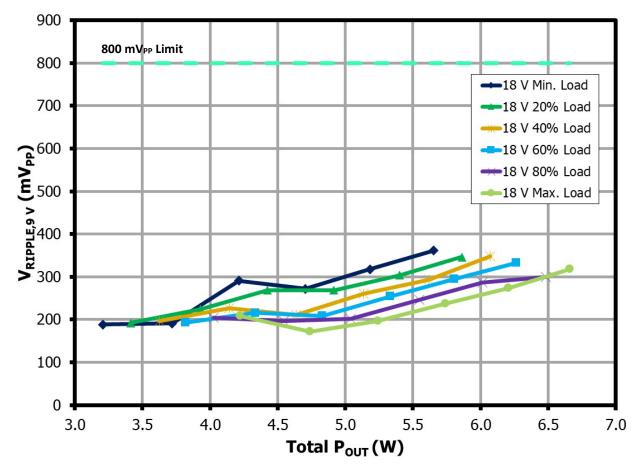

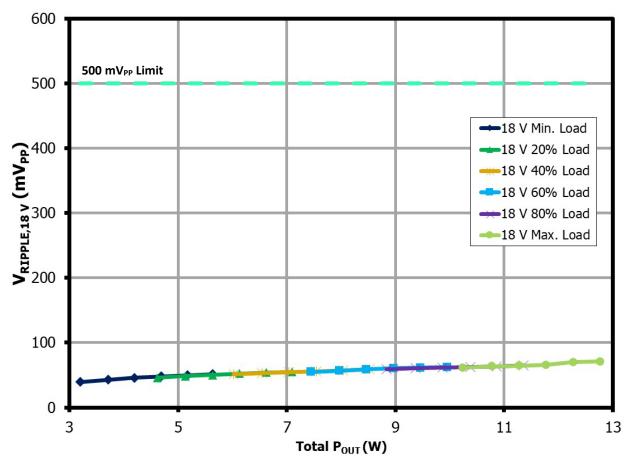

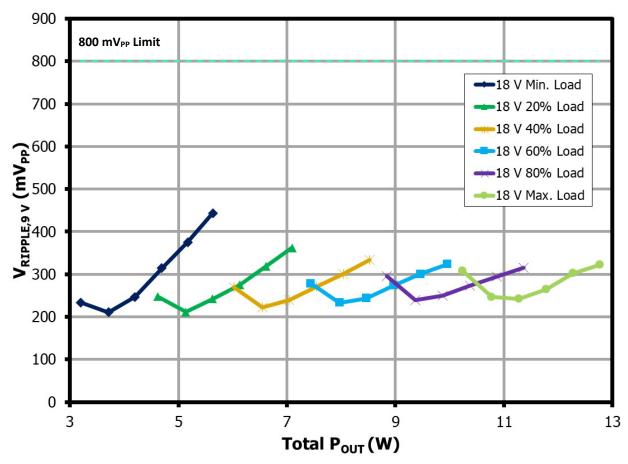

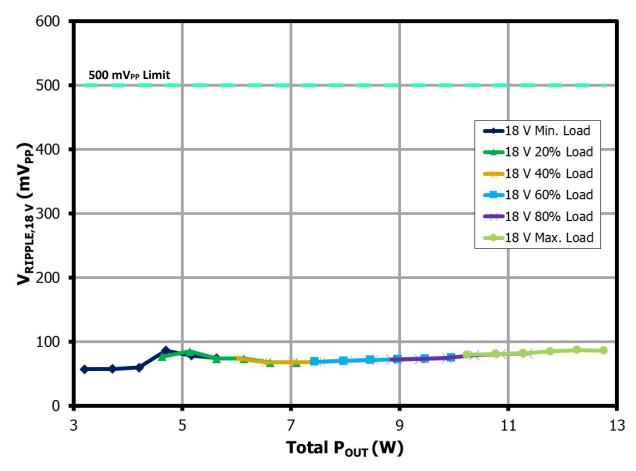

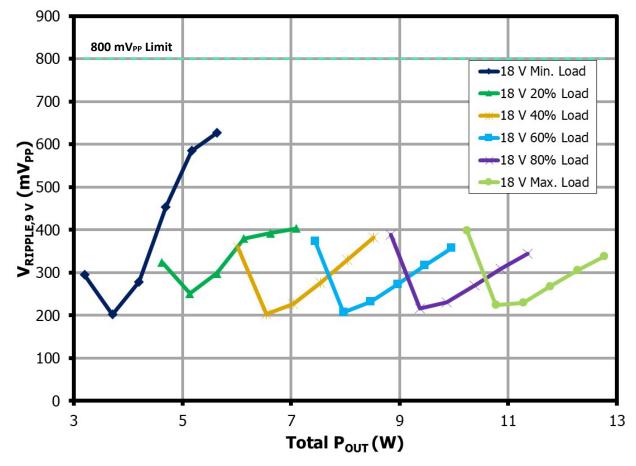

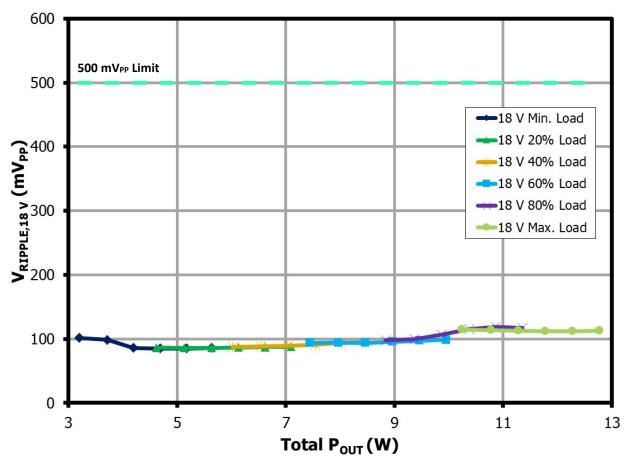

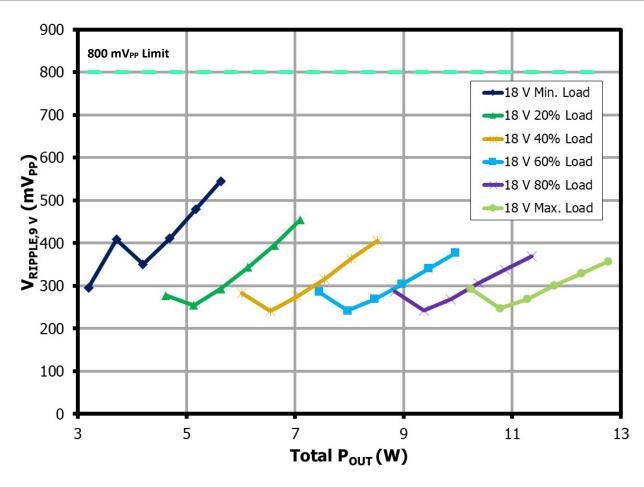

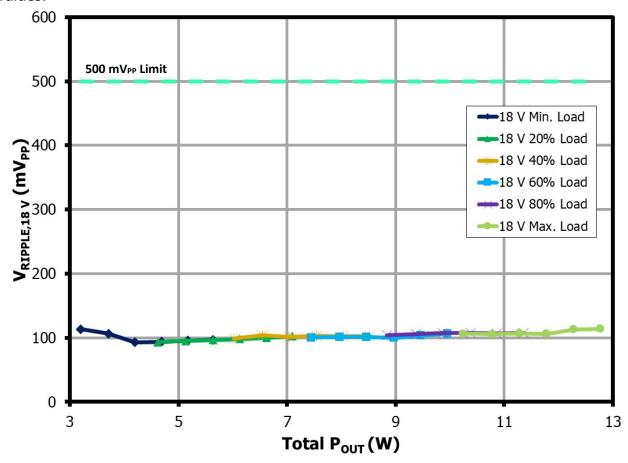

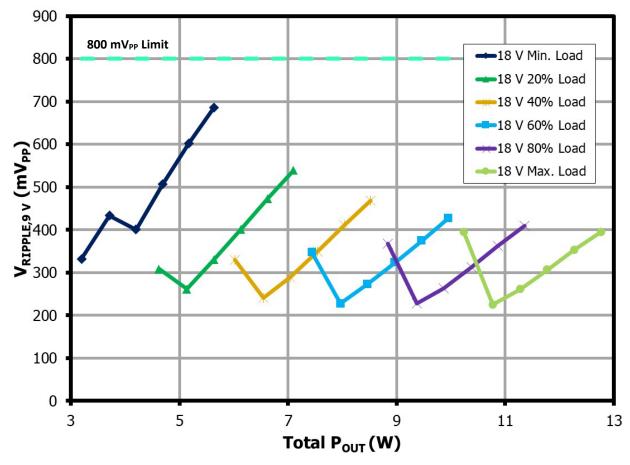

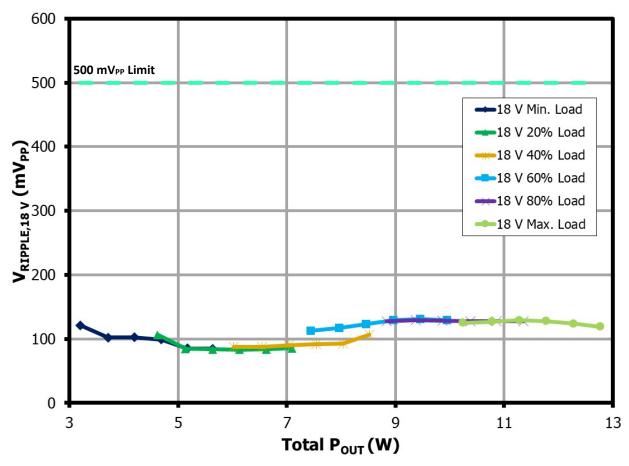

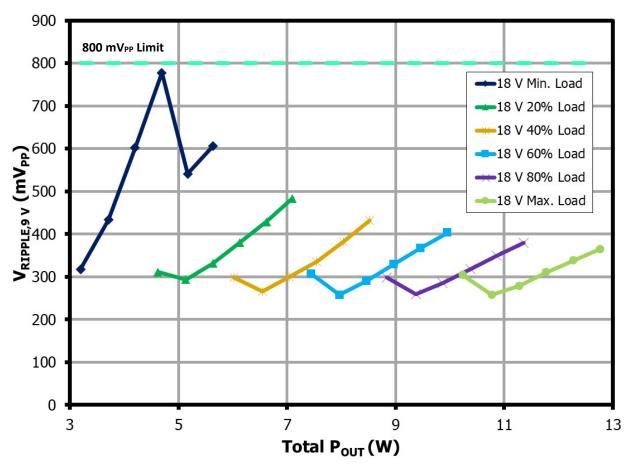

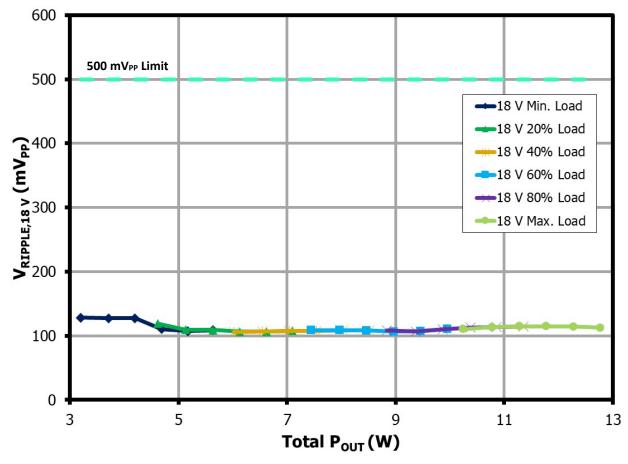

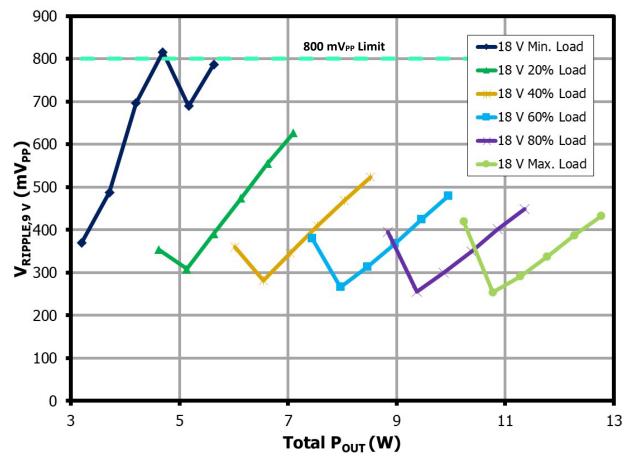

| 11.4.3   | Output Voltage Ripple vs. Load                        | 96  |

| 12 Outpu | ut Overload                                           | 112 |

|          | V Output Overload Capability                          |     |

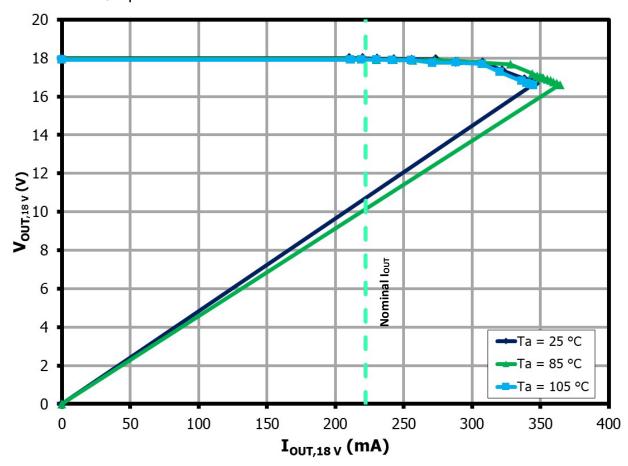

| 12.1.1   | 30 V <sub>DC</sub> Input                              | 112 |

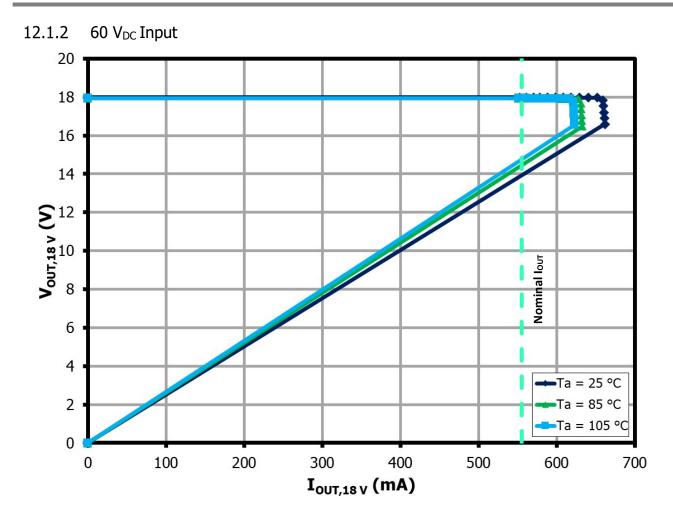

|          | 60 V <sub>DC</sub> Input                              |     |

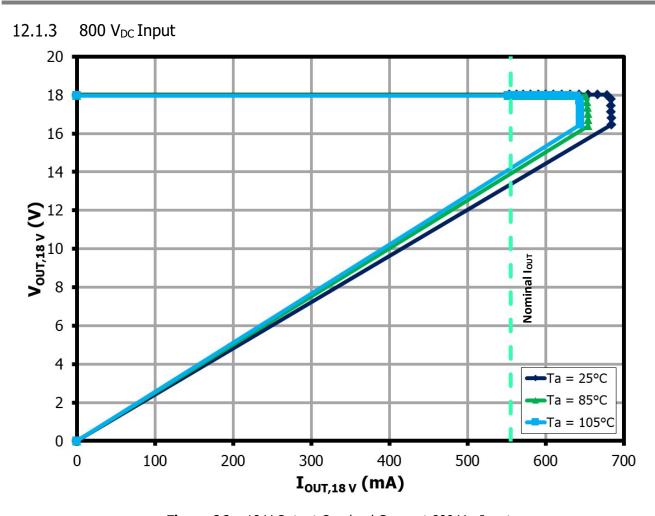

| 12.1.3   | 800 V <sub>DC</sub> Input                             | 114 |

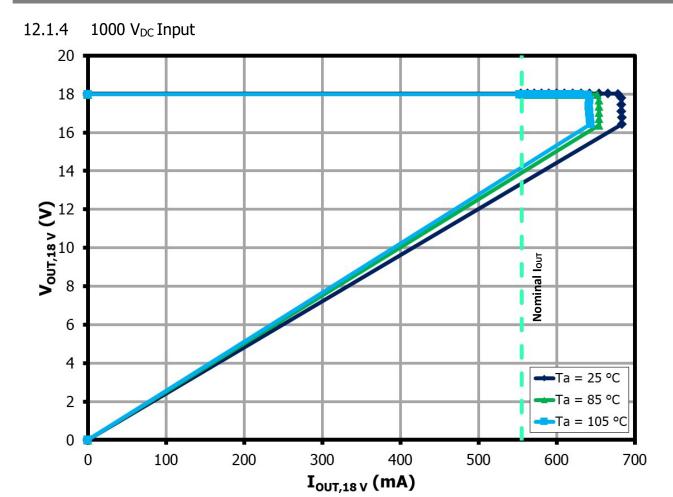

| 12.1.4   | 1000 V <sub>DC</sub> İnput                            | 115 |

|          | ion History                                           |     |

|          |                                                       |     |

#### **Disclaimer:**

The statements, technical information and recommendations contained herein are believed to be accurate as of the date hereof. All parameters, numbers, values and other technical data included in the technical information were calculated and determined to our best knowledge in accordance with the relevant technical norms (if any). They may base on assumptions or operational conditions that do not necessarily apply in general. We exclude any representation or warranty, express or implied, in relation to the accuracy or completeness of the statements, technical information and recommendations contained herein.

No responsibility is accepted for the accuracy or sufficiency of any of the statements, technical information, recommendations, or opinions communicated and any liability for any direct, indirect or consequential loss or damage suffered by any person arising therefrom is expressly disclaimed.

#### 1 Introduction

This engineering report describes a 13 W dual output automotive power supply. It is intended for use in 800 V battery system electric vehicles supporting an ultra-wide input range of 30  $V_{DC}$  to 1000  $V_{DC}$ . This design utilizes the 1700 V rated INN3949CQ IC from the InnoSwitch3-AQ family of IC's.

In a typical configuration the 9 V output provides an emergency backup power rail for the control power of the main traction inverter (functional safety requirement for loss of 12 V), the 18 V output provides gate power.

The design provides reinforced isolation both from the High Voltage DC (HVDC) input to the 18 V and 9 V outputs by observing required creepage and clearances as indicated in IEC 60664 parts 1 and 4. Basic isolation is provided between the 18 V and 9 V outputs.

Included in this document are the power supply design specifications, schematic diagram, bill of materials (BOM), magnetics documentation, printed circuit board (PCB) layout and performance data.

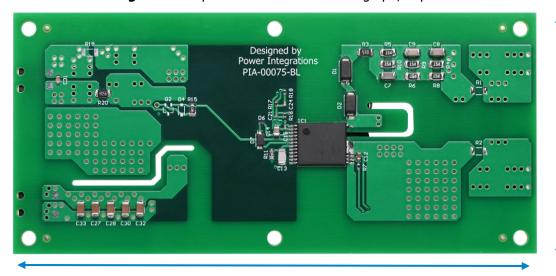

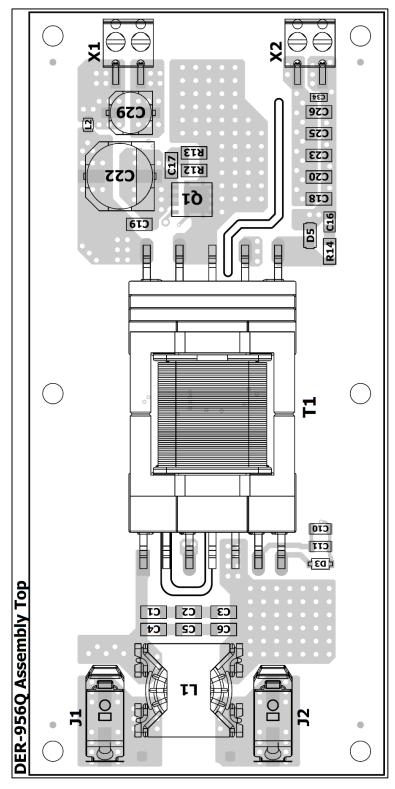

**Figure 1** – Populated Circuit Board Photograph, Entire Assembly.

**Figure 2 –** Populated Circuit Board Photograph, Top.

54 mm board width

116 mm board length

**Figure 3** – Populated Circuit Board Photograph, Bottom.

Figure 4 - Populated Circuit Board Photograph, Side.

The regulated 18 V output can deliver 10 W continuously at an input voltage range of 60  $V_{DC}$  to 1000  $V_{DC}$  which can be used to provide gate power for current generation of SiC MOSFETs.

At 30  $V_{DC}$  input, the power capability of 18 V output is reduced to 4 W, enough for startup where the inverter is not being driven. The cross regulated 9 V output can deliver 3 W of power from 30  $V_{DC}$  to 1000  $V_{DC}$  input voltage, providing backup power to maintain inverter operation in the event of the 12 V system failure (functional safety requirement).

The InnoSwitch3-AQ maintains necessary regulation by directly sensing the output voltage and providing fast, accurate feedback to the primary-side via FluxLink. Secondary-side control also enables the use of synchronous rectification improving the overall efficiency compared to diode rectification thus saving cost and space by eliminating heat sinking.

## **Design Specifications**

The table below represents the minimum acceptable performance of the design. The actual performance of the design is listed in the results section.

### 2.1 Electrical Specifications

| Description                                                                 | Symbol                         | Min. | Тур. | Max. | Units    |

|-----------------------------------------------------------------------------|--------------------------------|------|------|------|----------|

| Input Parameters                                                            |                                |      |      |      |          |

| Positive DC Link Input Voltage Referenced to HV-                            | HV+                            | 30   | 800  | 1000 | $V_{DC}$ |

| Operating Switching Frequency                                               | f <sub>SW</sub>                | 25   | 33   | 56   | kHz      |

| Output Parameters                                                           |                                |      |      |      |          |

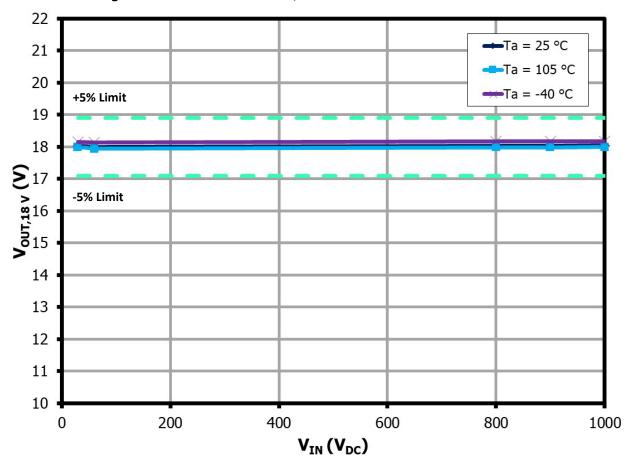

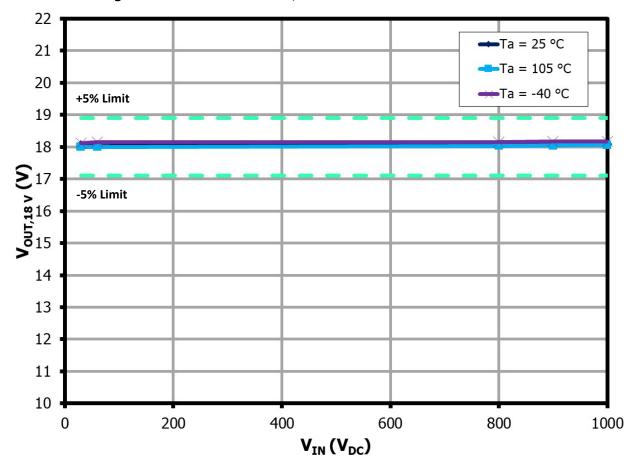

| 18 V Output                                                                 |                                |      |      |      |          |

| Output Voltage                                                              | <b>V</b> OUT (18 V)            | 17.1 | 18   | 18.9 | $V_{DC}$ |

| Load and Line Regulation                                                    | <b>V</b> <sub>REG (18 V)</sub> | -5   |      | +5   | %        |

| Output Voltage Ripple Measured on Board                                     | V <sub>RIPPLE (18 V)</sub>     |      | 500  |      | mV       |

| Output Overshoot / Output Undershoot                                        | ΔV <sub>OUT (18 V)</sub>       |      | ±5   |      | %        |

| Output Current                                                              | I <sub>OUT (18 V)</sub>        | 166  | 555  | 610  | mA       |

| Continuous Output Power                                                     | P <sub>OUT(18 V)</sub>         | 3    | 10   |      | W        |

| 9 V Output                                                                  |                                |      |      |      |          |

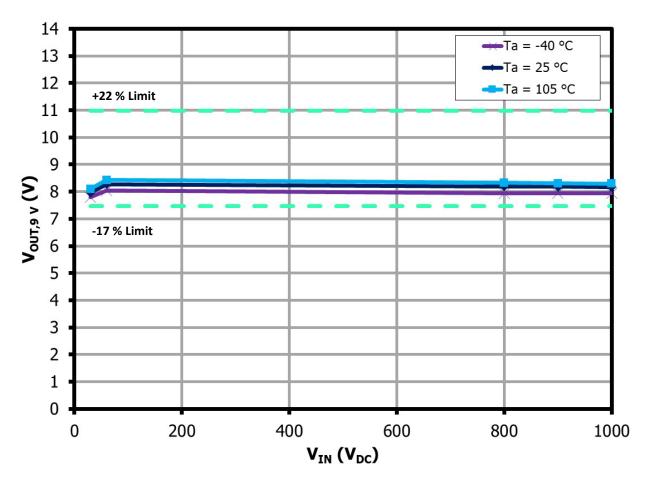

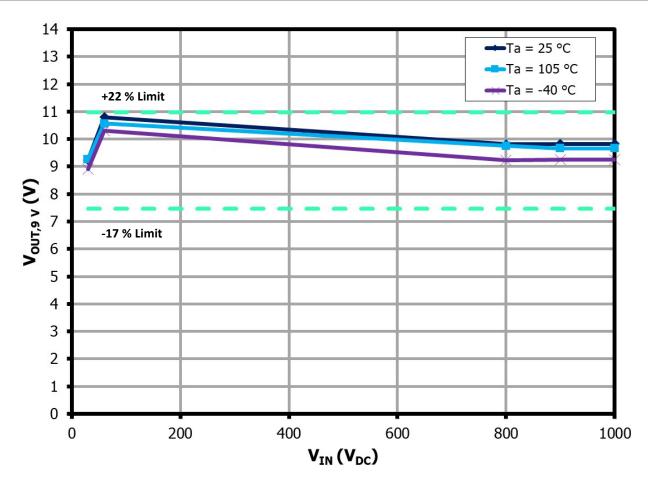

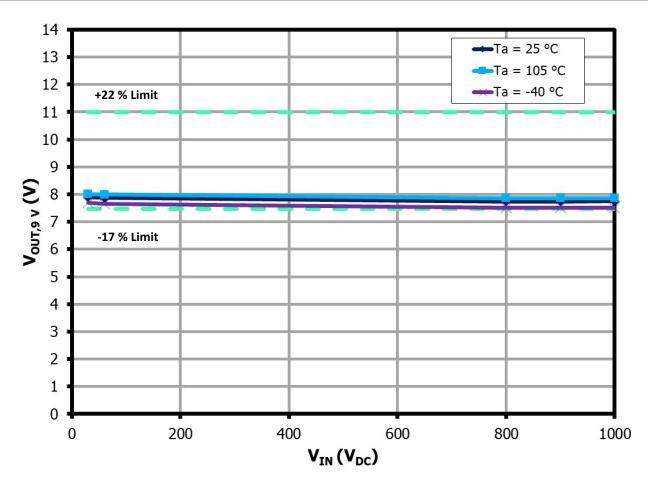

| Output Voltage                                                              | <b>V</b> OUT (9 V)             | 7.5  | 9    | 11   | $V_{DC}$ |

| Load and Line Regulation                                                    | <b>V</b> <sub>REG (9 V)</sub>  | -17  |      | +22  | %        |

| Output Voltage Ripple Measured on Board                                     | VRIPPLE (9 V)                  |      | 800  |      | mV       |

| Output Overshoot / Output Undershoot                                        | <b>ΔV</b> <sub>OUT (9 V)</sub> | -20  |      | +7   | %        |

| Output Current                                                              | <b>I</b> OUT (9 V)             | 22   |      | 333  | mA       |

| Continuous Output Power                                                     | <b>P</b> <sub>OUT(9 V)</sub>   | 0.2  |      | 3    | W        |

| Total Output Power Derating                                                 |                                |      |      |      |          |

| Continuous Output Power at 30 V <sub>DC</sub> Input                         | P <sub>OUT</sub>               |      |      | 7    | W        |

| Continuous Output Power at 60 V <sub>DC</sub> to 1000 V <sub>DC</sub> Input |                                |      |      | 13   | W        |

**Table 1** – Electrical Requirements.

#### 2.2 Isolation Coordination

| Description                                                           | Symbol                         | Min. | Тур. | Max. | Units           |

|-----------------------------------------------------------------------|--------------------------------|------|------|------|-----------------|

| Maximum Blocking Voltage of INN3949CQ                                 | BV <sub>DSS</sub>              |      |      | 1700 | V               |

| System Voltage                                                        | V <sub>SYSTEM</sub>            |      |      | 1202 | V               |

| Working Voltage                                                       | $V_{WORKING}$                  |      |      | 1000 | V               |

| Pollution Degree                                                      | PD                             |      |      | 2    |                 |

| CTI for FR4                                                           | CTI                            | 175  |      | 399  |                 |

| Rated Impulse Voltage                                                 | $oldsymbol{V}_{IMPULSE}$       |      |      | 2.5  | kV              |

| Altitude Correction Factor for h <sub>a</sub>                         | C <sub>ha</sub>                |      |      | 1.59 |                 |

| Technical Cleanliness Requirement                                     |                                |      |      | 0.6  | mm              |

| Basic Clearance Distance Requirement                                  | CLR <sub>BASIC</sub>           | 3.0  |      |      | mm              |

| Reinforced Clearance Distance Requirement                             | CLRREINFORCED                  | 5.4  |      |      | mm              |

| Basic Creepage Distance Requirement for PCB                           | CPG <sub>BASIC(PCB)</sub>      | 5.6  |      |      | mm              |

| Reinforced Creepage Distance Requirement for PCB                      | CPG <sub>REINFORCED(PCB)</sub> | 10.6 |      |      | mm              |

| Isolation Test Voltage Between Primary and Secondary-<br>Side for 60s | V <sub>ISO</sub>               | 5000 |      |      | $V_{PK}$        |

| Partial Discharge Test Voltage                                        | V <sub>PD_TEST</sub>           | 1803 |      |      | $V_{\text{PK}}$ |

**Table 2** – Isolation Requirements<sup>3</sup>.

## 2.3 Environmental Specifications

| Description           | Symbol | Min. | Тур. | Max. | Units |

|-----------------------|--------|------|------|------|-------|

| Ambient Temperature   | Ta     | -40  |      | 105  | °C    |

| Altitude of Operation | ha     |      |      | 5500 | m     |

| Relative Humidity     | RH     |      |      | 85   | %     |

**Table 3** – Environmental Requirements.

<sup>&</sup>lt;sup>3</sup> Clearance and creepage distances are derived from IEC 60664-1 and IEC 60664-4.

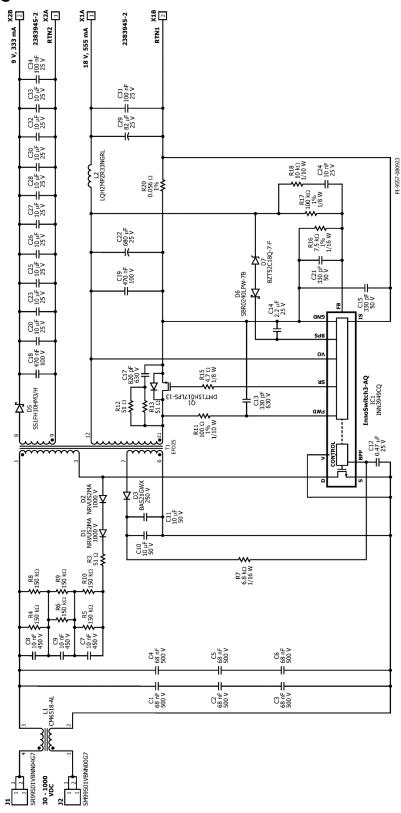

## 3 **Schematic**

**Figure 5** – DER-956Q Schematic.

## 4 **Circuit Description**

#### 4.1 *Input Filter*

The automotive inverter environment is harsh, characterized by high dv/dt and di/dt from the switching action of the power modules. Large common mode currents are generated across the isolation barrier of the power supply which in turn can interfere with both the power supply operation, other inverter blocks and measurement signal integrity. The input common mode choke L1 together with the bypass capacitors C1 to C6 helps filter unwanted noise and prevents them from affecting the overall performance of the design.

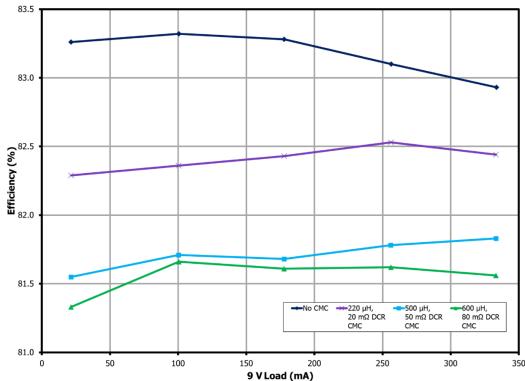

Common mode inductor L1 was selected such that the reference board would be able to withstand the Power Integrations' internal "Resistance to ripple on high voltage network" test. The test injects high frequency ripple on the high voltage input to simulate the actual DC link capacitor ripple in a traction inverter. The final value of L1 will depend on the final design or application requirement. The higher the noise, the higher the inductance of L1 should be. However, consideration should be given between inductance value and the DC resistance (DCR) which has an impact on the overall efficiency of the design. Figure 6 shows how DCR of the common mode choke impacts the overall efficiency of the reference board.

Capacitor C1 to C6 bypass capacitors were selected so as not to exceed 65% of their voltage rating as well as to maintain enough pad-to-pad distance to meet creepage and clearance requirements.

Figure 6 – DCR Effect on Efficiency at 1000 V<sub>DC</sub> Input (No Input Noise) and 18 V at Maximum Load.

#### 4.2 *High-Voltage Side Circuit*

The design uses a flyback converter to provide two isolated low voltage outputs from the high-voltage input. One end of the flyback transformer T1 primary winding is connected to the high voltage DC input while the other end is connected to the drain terminal of the integrated 1700 V power MOSFET inside the INN3949CQ IC1.

Primary clamp circuit formed by diodes D1, D2, resistors R4, R5, R6, R8, R9, R10 and capacitors C7, C8, C9 limits the peak drain-source voltage of IC1 at the instant the switch inside IC1 turns off. As compared with the traditional RCD clamp, two surface mount AEC-Q qualified diodes were used in series to meet the creepage and clearance requirements as well as to ensure that the voltage across each diode would not exceed 70% of their rating. The resistor network helps to dissipate the energy stored in the leakage reactance of transformer T1. Snubber resistors were selected such that 80% of their voltage rating would not be exceeded while maintaining power dissipation of below 50%. Cooling area for the snubber resistors were also considered to ensure operating temperature would be at acceptable level.

The IC is self-starting, using an internal high-voltage current source to charge the BPP pin capacitor C12 when the DC input voltage is first applied. The INN3949CQ is guaranteed to start-up from 30 V but typically will start below this level.

During normal operation, the primary-side block is powered by the auxiliary winding of transformer T1. The output of the auxiliary (or bias) winding is rectified using diode D3 and filtered using capacitors C10 and C11. Resistor R7 limits the BPP pin current of IC1 to a value sufficient for normal operation without incurring excessive losses.

In this design the input primary under and overvoltage features were disabled by connecting the V pin to SOURCE pin. This approach does not require the voltage sensing resistor chain used in setting the under or overvoltage feature of IC1 thus saving cost and space. However, with no undervoltage feature the output may fail to reach regulation at voltages < 40  $V_{DC}$  with high output load current, causing the outputs to rise but fail to reach regulation (hiccup). The timing is determined by the auto-restart (AR) feature, giving a 50 ms start-up attempt followed by a 2 s off time.

If this is not acceptable on the target design or application, then the undervoltage feature can be implemented. Please refer to the datasheet for the recommended circuit and design guide.

#### 4.3 Low Voltage Circuit Side

The secondary side, regulated 18 V output, of the INN3949CQ IC provides output voltage, output current sensing and gate drive for the MOSFET providing synchronous rectification (SR). The voltage across the 18 V winding of the transformer T1 is rectified by MOSFET Q1 and filtered by capacitor C19 and C22. High frequency ringing during switching is reduced by the RC snubber formed by resistors R12, R13 and capacitor C17.

Switching of Q1 is controlled by the secondary-side controller inside IC1. Control is based on the winding voltage sensed by the FWD pin via resistor R11. Capacitor C13 reduces voltage

spike on the FWD pin to ensure that voltage seen by this pin won't exceed its maximum rating of 150 V.

In continuous conduction mode operation, the primary-side power MOSFET is turned off just prior to the secondary-side controller commanding a new switching cycle from the primary. In discontinuous mode the SR MOSFET is turned off when the voltage drop across it falls below a certain threshold of approximately  $V_{SR(TH)}$ . Secondary-side control of the primary-side power MOSFET avoids any possibility of cross conduction of the two switches and ensures reliable synchronous rectifier operation.

The secondary side of the IC is self-powered from either the secondary winding forward voltage (via R11 and the FWD pin) or by the output voltage (via the V pin). In both cases energy is used to charge the decoupling capacitor C14 via an internal regulator.

Resistors R17 and R16 form a voltage divider network that senses the output voltage. The INN3949CQ IC has an FB pin internal reference of 1.265 V. Capacitor C21 provides decoupling from high frequency noise affecting power supply operation. C24 and R18 is a feedforward network to speed up the response time and lower the output ripple.

Output current is sensed by monitoring the voltage drop across resistor R20. The resulting current measurement is filtered with the decoupling capacitor C15 and monitored across the IS and GND pins. An internal current sense threshold of around 35 mV is used to minimize losses. Once the threshold is exceeded, the INN3949CQ IC1 will enter auto-restart (hiccup) operation until the load current is reduced below the threshold.

Similarly, the voltage across the 9 V cross regulated winding of transformer T1 is rectified by the freewheeling diode D5 and is filtered by the capacitors C18, C20, C23, C25, C26, C27, C28, C30, C32, C33. Regulation of the 9 V output depends on good coupling (low leakage inductance) to the 18 V output, this is addressed in the transformer design.

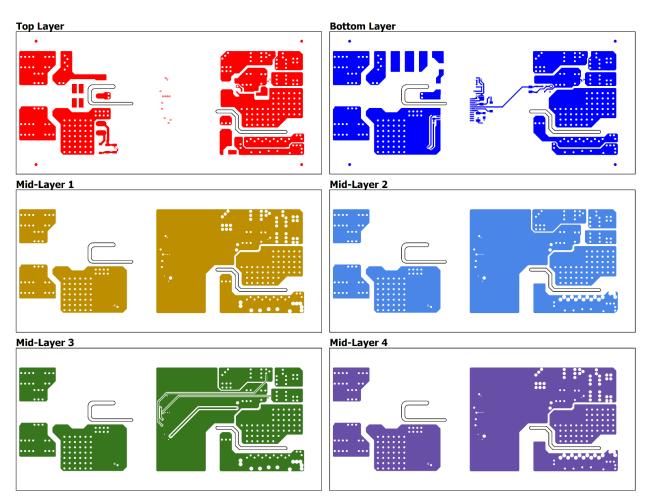

## 5 **PCB Layout**

Layers: Six (6) (typical for traction inverter control board)

Board Material: FR4

Board Thickness: 1.6 mm

Copper Weight: 2 oz

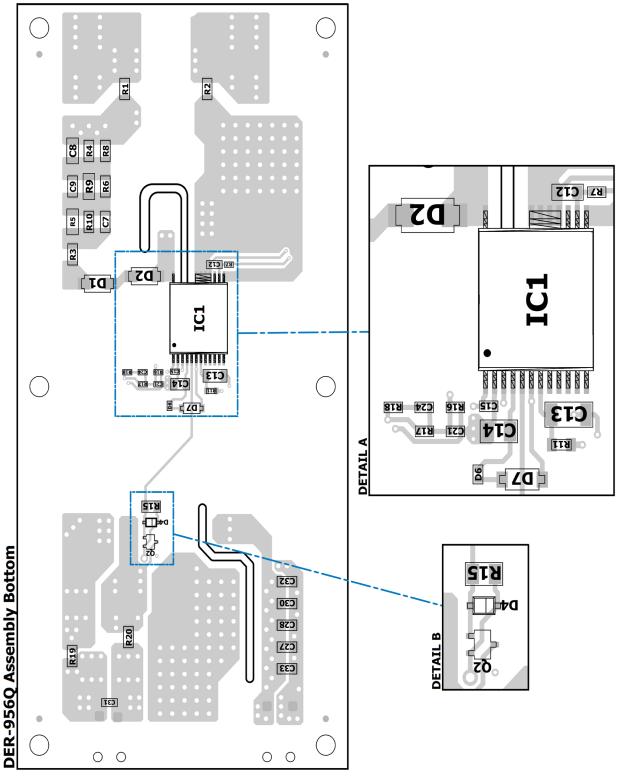

Figure 7 - DER-956Q Board Layout.

Figure 8 - DER-956Q Board Assembly (Top).

Figure 9 - DER-956Q Board Assembly (Bottom).

# **6 Bill of Materials**

| Item | Qty. | Designator                                        | Description                                                                                                        | MFR Part Number              | Manufacturer       |

|------|------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------|

| 1    | 6    | C1, C2, C3, C4,<br>C5, C6                         | Multilayer Ceramic Capacitors MLCC - SMD/SMT 500 V 0.068 µF X7R 1206 10% AEC-Q200                                  | C1206C683KCRACAUTO           | KEMET              |

| 2    | 3    | C7, C8, C9                                        | Multilayer Ceramic Capacitors MLCC - SMD/SMT CGA<br>1206 450 V 0.01 μF C0G 5% AEC-Q200                             | CGA5L4C0G2W103J160AA         | TDK                |

| 3    | 2    | C10, C11                                          | Multilayer Ceramic Capacitors MLCC - SMD/SMT 1206<br>50 VDC 10 μF 10% X7R AEC-Q200                                 | CGA5L1X7R1H106K160AE         | TDK                |

| 4    | 1    | C12                                               | Multilayer Ceramic Capacitors MLCC - SMD/SMT CGA<br>0603 25 V 0.47 μF X7R 10% AEC-Q200                             | CGA3E3X7R1E474K080AB         | TDK                |

| 5    | 1    | C13                                               | Multilayer Ceramic Capacitors MLCC - SMD/SMT CGA<br>1206 630 V 330 pF C0G 5% AEC-Q200                              | CGA5C4C0G2J331J060AA         | TDK                |

| 6    | 2    | C15, C21                                          | Multilayer Ceramic Capacitors MLCC - SMD/SMT 50 V<br>330 pF C0G 0402 5% AEC-Q200                                   | AC0402JRNPO9BN331            | YAGEO              |

| 7    | 1    | C17                                               | Multilayer Ceramic Capacitors MLCC - SMD/SMT 1206<br>630 V 820 pF 5% COG AEC-Q200                                  | C1206C821JBGACAUTO           | KEMET              |

| 8    | 0    | C16                                               | Multilayer Ceramic Capacitors MLCC - SMD/SMT 0805<br>450 V 470 pF 5% SOFT COG AEC-Q200                             | CGA4C4C0G2W471J060AE         | TDK                |

| 9    | 1    | C14                                               | Multilayer Ceramic Capacitors MLCC - SMD/SMT 0805<br>25 VDC 2.2 µF 10% X7R AEC-Q200                                | TMK212B7225KGHT              | Taiyo Yuden        |

| 10   | 1    | C22                                               | Aluminum Organic Polymer Capacitors                                                                                | EEH-ZS1E681UP                | Panasonic          |

| 11   | 1    | C24                                               | Multilayer Ceramic Capacitors MLCC - SMD/SMT CGA<br>0402 25 V 0.01 μF X7R 10% AEC-Q200                             | CGA2B2X7R1E103K050BA         | TDK                |

| 12   | 1    | C29                                               | Aluminum Organic Polymer Capacitors                                                                                | A768EB826M1ELAS036           | KEMET              |

| 13   | 2    | C31, C34                                          | Multilayer Ceramic Capacitors MLCC - SMD/SMT CGA 0603 25 V 0.1 µF X7R 10% AEC-Q200                                 | CGA3E2X7R1E104K080AA         | TDK                |

| 14   | 2    | C18, C19                                          | Multilayer Ceramic Capacitors MLCC - SMD/SMT 1206<br>100 VDC 0.47 μF 10% X7R AEC-Q200                              | HMK316B7474KLHT              | Taiyo Yuden        |

| 15   | 9    | C20, C23, C25,<br>C26, C27, C28,<br>C30, C32, C33 | Multilayer Ceramic Capacitors MLCC - SMD/SMT 1206 25 VDC 10 $\mu$ F 10% X7R AEC-Q200                               | CGA5L1X7R1E106K160AC         | TDK                |

| 16   | 2    | D1, D2                                            | Rectifiers 1000 V 1.5 A High Efficiency Rectifier                                                                  | NRVUS2MA                     | ON Semi            |

| 17   | 1    | D3                                                | Diodes - General Purpose, Power, Switching DIODE-GP POWER SWITCHING                                                | BAS21GWX                     | Nexperia           |

| 18   | 0    | D4                                                | Schottky Diodes & Rectifiers 5 μA 20 Volt 15 A IFSM                                                                | SD103CWS-E3-08               | Vishay             |

| 19   | 1    | D5                                                | Schottky Diodes & Rectifiers If 1 A Vrrm 100 V                                                                     | SS1FH10HM3/H                 | Vishay             |

| 20   | 1    | D6                                                | Schottky Diodes & Rectifiers SBR Diode X1-DFN1006-<br>2/SWP T&R 10K                                                | SBR0240LPW-7B                | Diodes, Inc.       |

| 21   | 1    | D7                                                | Zener Diode SOD123 T&R 3K                                                                                          | BZT52C18Q-7-F                | Diodes, Inc.       |

| 22   | 1    | IC1                                               | CV/CC QR Flyback Switcher IC with Integrated 1700 V<br>Switch and FluxLink Feedback for Automotive<br>Applications | INN3949CQ                    | Power Integrations |

| 23   | 1    | J1                                                | TERM BLOCK 1POS SIDE ENTRY SMD RED                                                                                 | SR99S01VBNN04G7              | METZ CONNECT       |

| 24   | 1    | J2                                                | TERM BLOCK 1POS SIDE ENTRY SMD BLACK                                                                               | SM99S01VBNN00G7              | METZ CONNECT       |

| 25   | 1    | L1                                                | Input Common Mode Choke                                                                                            | CM6518-AL                    | Coilcraft          |

| 26   | 1    | L2                                                | Fixed Inductors 0806 0.33 $\mu\text{H}$ 30% 2200 mA 0.18 $\Omega$                                                  | LQH2MPZR33NGRL               | Murata             |

| 27   | 1    | Q1                                                | N-CHANNEL MOSFET BVDSS: 150 V 9.4 A 17.5 m $\Omega$                                                                | DMT15H017LPS-13 <sup>4</sup> | Diodes, Inc.       |

| 28   | 0    | Q2                                                | P-CHANNEL MOSFET BVDSS:                                                                                            | DMG1013UWQ-7                 | Diodes, Inc.       |

| 29   | 3    | R3, R12, R13                                      | Thick Film Resistors - SMD 51 $\Omega$ ¼ W 1206 5% AEC-Q200                                                        | AC1206JR-0751RL              | YAGEO              |

| 30   | 0    | R14                                               | Thick Film Resistors - SMD 51 $\Omega$ ¼ W 1206 5% AEC-Q200                                                        | AC1206JR-0751RL              | YAGEO              |

| 31   | 6    | R4, R5, R6, R8,<br>R9, R10                        | Thick Film Resistors - SMD 1206 150 k $\Omega$ 5% AEC- ERJ-8GEYJ154V Q200                                          |                              | Panasonic          |

| 32   | 1    | R7                                                | Thick Film Resistors - SMD 1/16 W 6.8 kΩ 5%                                                                        | CRCW04026K80JNED             | Vishay             |

| 33   | 1    | R11                                               | Thick Film Resistors - SMD 100 $\Omega$ 100 mW 0603 1% AEC-Q200                                                    | AC0603FR-13100RL             | YAGEO              |

<sup>&</sup>lt;sup>4</sup> DMT15H017LPS-13 is qualified for AEC-Q101 reliability test only but not fully qualified for all AEC-Q criteria.

Power Integrations, Inc.

| 34 | 1 | R15         | Thick Film Resistors - SMD 4.7 $\Omega$ 1/8 mW 0805 5% AEC-Q200        | AC0805JR-074R7L   | YAGEO              |

|----|---|-------------|------------------------------------------------------------------------|-------------------|--------------------|

| 35 | 1 | R16         | Thick Film Resistors - SMD 7.5 k $\Omega$ 62.5 mW 0402 1% AEC-Q200     | AC0402FR-077K5L   | YAGEO              |

| 36 | 1 | R17         | Thick Film Resistors - SMD 0.125 W 100 k $\Omega$ 1% 200ppm Anti-Surge | SG73S1ETTP1003F   | KOA                |

| 37 | 1 | R18         | Thick Film Resistors - SMD 0402 5% 10 $k\Omega$ Anti-Sulfur AEC-Q200   | ERJ-U02J103X      | Panasonic          |

| 38 | 1 | R20         | Current Sense Resistors - SMD 0.056 $\Omega$ 1% 1/4 W                  | RL1206FR-070R056L | YAGEO              |

| 39 | 2 | R1, R2, R19 | Thick Film Resistors - SMD 0 $\Omega$ 250 mW (1/4 W) 1206 $1\%$        | AF1206JR-070RL    | YAGEO              |

| 40 | 1 | T1          | 13 W Power Transformer                                                 |                   | Power Integrations |

| 41 | 1 | T1-Core     | 3C95 Ferrite Core                                                      |                   | Ferroxcube         |

| 42 | 1 | T1-Bobbin   | Customized bobbin                                                      |                   | Power Integrations |

| 43 | 2 | X1, X2      | TERMI-BLOK SMD MOUNT 180_2P_3.81                                       | 2383945-2         | TE                 |

| 44 | 1 | Z1          | Printed Circuit Board, PIA-00075-TL                                    |                   | Power Integrations |

**Table 4** – DER-956Q Bill of Materials<sup>5</sup>.

<sup>&</sup>lt;sup>5</sup> All components are AEC-Q qualified except for connectors, T1 and L1.

¥

## 7 Transformer Specification

## 7.1 Electrical Diagram

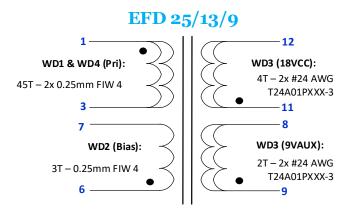

**Figure 10** – Transformer Electrical Diagram.

## 7.2 Electrical Specification

| Parameter                     | Conditions                                                                                                                                                                         | Min. | Тур.  | Max. | Unit |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| Power                         | Output power secondary-side                                                                                                                                                        |      |       | 13   | W    |

| Input Voltage Vdc             | Flyback topology                                                                                                                                                                   | 30   | 800   | 1000 | V    |

| Switching Frequency           | Flyback topology                                                                                                                                                                   | 25   |       | 56   | kHz  |

| Duty Cycle                    | Flyback topology                                                                                                                                                                   | 1.8  |       | 65.2 | %    |

| Np:Ns                         |                                                                                                                                                                                    |      | 11.25 |      |      |

|                               | WD1 (Pri)                                                                                                                                                                          |      |       | 390  |      |

|                               | WD2 (Bias)                                                                                                                                                                         |      |       | 170  |      |

| Rdc                           | WD3a (18 VCC)                                                                                                                                                                      |      |       | 11   | mΩ   |

| Ruc                           | WD3b (9 VAUX)                                                                                                                                                                      |      |       | 8    |      |

|                               | WD4 (Pri)                                                                                                                                                                          |      |       | 460  |      |

|                               | Primary side to bias side,<br>Measured at 1 V <sub>PK-PK</sub> , 100 kHz frequency, between pin 1 to pin<br>7, with pins 1 - 3 shorted and pins 6 - 7 shorted at 25 °C             |      |       | 20   |      |

| Coupling Capacitance          | Primary side to 18 VCC (Sec 1) side<br>Measured at 1 V <sub>PK-PK</sub> , 100 kHz frequency, between pin 1 to pin<br>12, with pins 1 - 3 shorted and pins 11 - 12 shorted at 25 °C |      |       | 35   | pF   |

|                               | Primary side to 9 VAUX (Sec 2) side<br>Measured at 1 V <sub>PK-PK</sub> , 100 kHz frequency, between pin 1 to pin<br>8, with pins 1 - 3 shorted and pins 8 - 9 shorted at 25 °C    |      |       | 20   |      |

| Primary Inductance            | Measured at 1 $V_{PK-PK}$ , 100 kHz frequency, between pin 1 to pin 3, with all other windings open at 25 °C                                                                       |      | 445   |      | μΗ   |

| Part to Part<br>Tolerance     | Tolerance of Primary Inductance                                                                                                                                                    | -5.0 |       | 5.0  | %    |

| Primary Leakage<br>Inductance | Measured at 1 V pk-pk, 100 kHz frequency between pin 1 to pin 3, with all other Windings shorted.                                                                                  |      |       | 7.5  | μΗ   |

**Table 5** – Transformer electrical specification.

## 7.3 Transformer Build Diagram

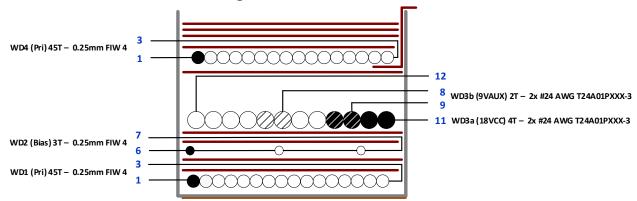

**Figure 11 –** Transformer Build Diagram.

#### 7.4 *Material List*

| Item | Description                                      | Qty  | UOM | Material                    | Manufacturer |

|------|--------------------------------------------------|------|-----|-----------------------------|--------------|

| [1]  | Bobbin: MCT-EFD25-N2 H7+5P                       | 1    | PC  | Phenolic                    | MyCoilTech   |

| [2]  | Core: EFD 25/13/9                                | 2    | PCS | 3C95<br>(or equivalent)     | Ferroxcube   |

| [3]  | WD1 (Pri): 0.25 mm FIW 4, Class F                | 2000 | mm  |                             | Elektrisola  |

| [4]  | WD4 (Pri): 0.25 mm FIW 4, Class F                | 2310 | mm  |                             | Elektrisola  |

| [5]  | WD2 (Bias): 0.25 mm FIW 4, Class F               | 176  | mm  |                             | Elektrisola  |

| [6]  | WD3a (18 VCC):<br>T24A01PXXX-3, AWG 24 PFA .003" | 500  | mm  | Copper Wire                 | Rubadue      |

| [7]  | WD3b (9 VAUX):<br>T24A01PXXX-3, AWG 24 PFA .003" | 320  | mm  |                             | Rubadue      |

| [8]  | 3M Polyimide 5413 Amber, width: 0.625in (15.9mm) | 360  | mm  | 3M157181<br>(or equivalent) | 3M           |

| [9]  | 0.51mm Teflon Tubing Class B                     | 30   | mm  | TFT20024<br>(or equivalent) | Alphawire    |

**Table 6 –** Transformer Bill of Materials.

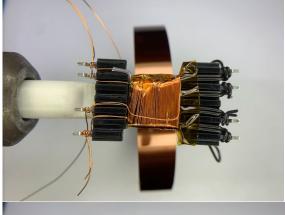

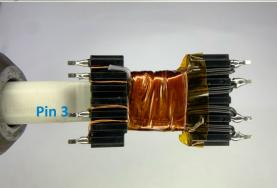

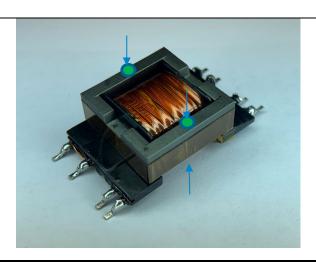

## 7.5 *Winding Illustrations*

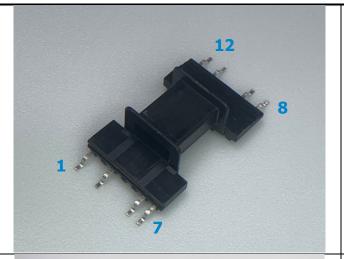

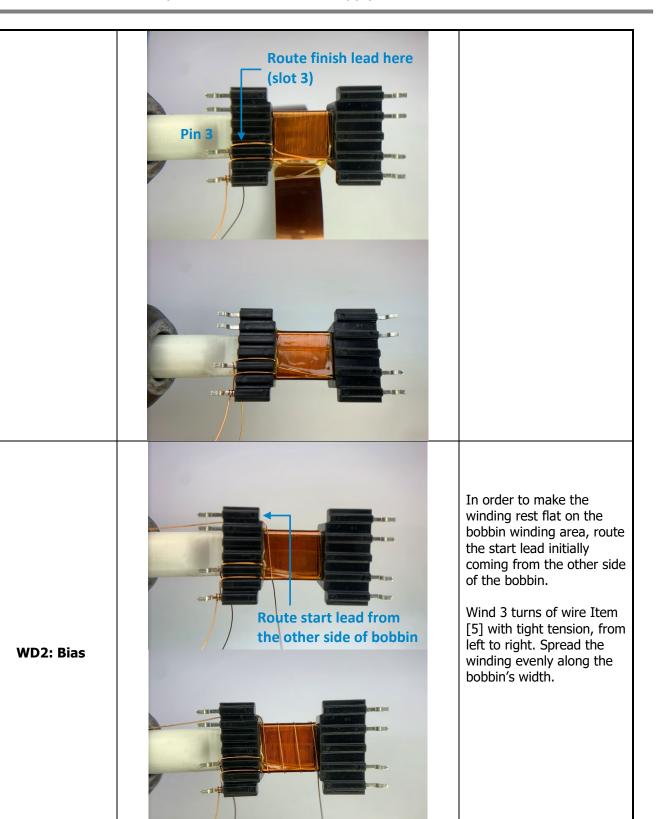

Start by removing the unused pins 2, 4, 5 and 10 of the bobbin (Item [1])

# Winding Preparation

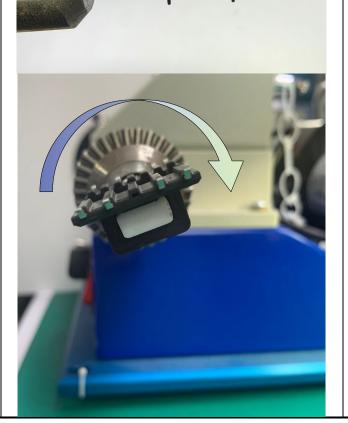

Position the bobbin on the mandrel such that the primary side (pins 1-7) of the bobbin is on the left side.

Winding direction is clockwise direction.

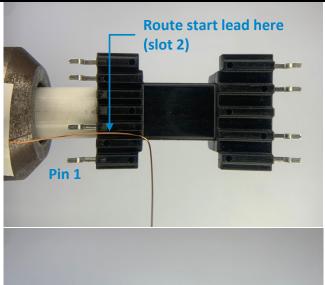

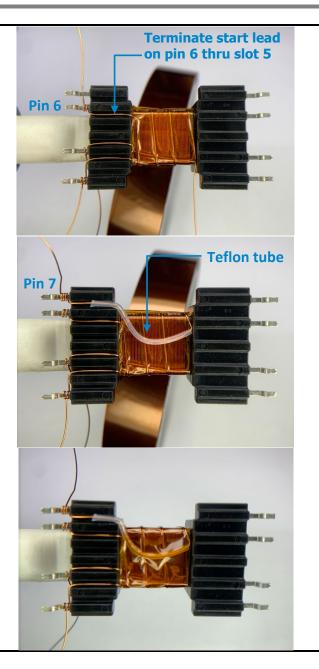

WD1: Pri

Route the start lead from pin 1 going to the bobbin thru slot 2 and then wind 45 turns of wire Item [3] with tight tension, from left to right. Spread the winding evenly along the bobbin's width.

Place 1 layer of tape (Item [8]) between the winding and the finish lead before terminating the finish lead to pin 3.

Route the finish lead on slot 3 going to pin 3.

Place 1 layer of tape (Item [8]) between the winding and the finish lead.

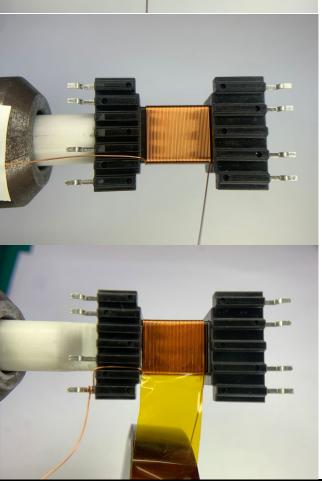

Before closing the layer of tape, terminate the start lead on Pin 6 and insert teflon tube Item [9] on the finish lead then terminate it to pin 7.

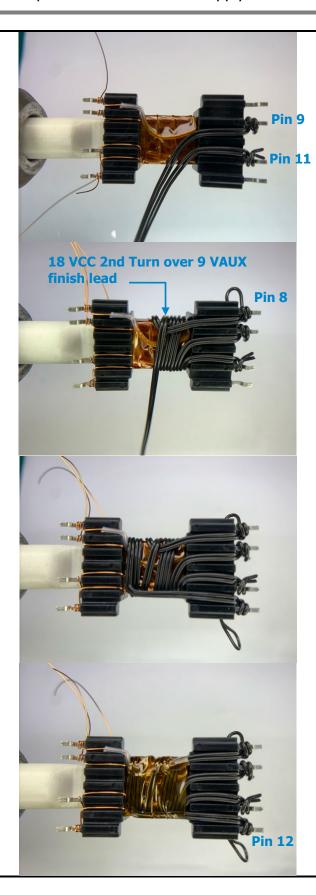

Use 2 strands of wire Item [7] for the 9 VAUX winding and start it at pin 9. Also use 2 strands of wire Item [6] for the 18 VCC winding and start it at pin 11.

Wind all wires together with tight tension, from right to left.

After 2 turns, fold the end of the bifilar 9 VAUX winding to the right then terminate it to pin 8 and continue to wind the 18 VCC bifilar winding for 2 more additional turns.

Place 1 layer of tape (Item [8]) to finish WD3.

WD3: 18 VCC and 9 VAUX

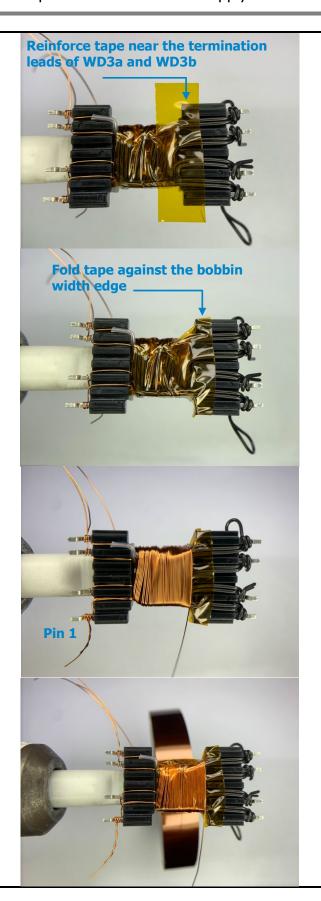

Before winding WD4, reinforce the insulation near the termination end of WD3 by placing 1 layer of tape (Item [8]) as shown.

Trim the reinforced tape and fold it flat against the bobbin width edge as shown.

Start at pin 1, wind 45 turns of wire Item [4] with tight tension, from left to right. Spread the winding evenly along the bobbin's width.

Place 1 layer of tape (Item [8]) between the winding and the finish lead before terminating the finish lead to pin 3.

WD4: Pri

Finish up by placing 3 layers of tape (Item [8]).

Solder all terminated pins (pin 1, 3, 6, 7, 8, 9, 11 and 12).

**Finishing**

Gap one of the core halves (item [2]) and fasten the core tightly to get 445  $\mu$ H  $\pm$  5% of inductance between pins 1 and 3.

In fastening the core, it is preferred to use glue instead of tape that is used in the illustration (see blue arrows for the preferred gluing points – 2 points on top and 2 points on the bottom.)

# **8 Transformer Design Spreadsheet**

|           |                                                                                            | D 031911 0       |       |           |       |                                                                                                           |

|-----------|--------------------------------------------------------------------------------------------|------------------|-------|-----------|-------|-----------------------------------------------------------------------------------------------------------|

| 1         | DCDC_InnoSwitch3AQ<br>_Flyback_012722;<br>Rev.3.2; Copyright<br>Power Integrations<br>2022 | INPUT            | INFO  | ОИТРИТ    | UNITS | InnoSwitch3-AQ Flyback Design<br>Spreadsheet                                                              |

| 2         | APPLICATION VARIABLE                                                                       | S                |       |           |       |                                                                                                           |

| 3         | VOUT                                                                                       | 18.00            |       | 18.00     | V     | Output Voltage                                                                                            |

| 4         | <b>OPERATING CONDITION</b>                                                                 | 1                |       |           |       |                                                                                                           |

| 5         | VINDC1                                                                                     | 1000.00          |       | 1000.00   | V     | Input DC voltage 1                                                                                        |

| 6         | IOUT1                                                                                      | 0.722            | 1     | 0.722     | A     | Output current 1                                                                                          |

| 7         | POUT1                                                                                      | 0.7 ==           | 1     | 13.00     | W     | Output power 1                                                                                            |

| 8         | EFFICIENCY1                                                                                |                  | †     | 0.85      | ***   | Converter efficiency for output 1                                                                         |

| 9         | Z_FACTOR1                                                                                  |                  | +     | 0.50      | -     | Z-factor for output 1                                                                                     |

| 11        | OPERATING CONDITION                                                                        | 2                | 1     | 0.50      | 1     | 2 140001 101 044946 1                                                                                     |

| 12        | VINDC2                                                                                     | 450.00           | T     | 450.00    | V     | Input DC voltage 2                                                                                        |

| 13        | IOUT2                                                                                      | 0.722            | +     | 0.722     | A     | Output current 2                                                                                          |

| 14        | POUT2                                                                                      | 0.722            | +     | 13.00     | W     | Output current 2 Output power 2                                                                           |

| 15        | EFFICIENCY2                                                                                |                  | +     | 0.85      | VV    | Converter efficiency for output 2                                                                         |

| 16        | Z_FACTOR2                                                                                  |                  | +     | 0.50      | +     | Z-factor for output 2                                                                                     |

| <b>69</b> | PRIMARY CONTROLLER S                                                                       | CELECTION        | 1     | 0.50      | 1     | Z-ractor for output z                                                                                     |

|           |                                                                                            |                  | Т     | CTANDADD  |       | Davidas armont limitana da                                                                                |

| 70        | ILIMIT_MODE                                                                                | STANDARD         | 1     | STANDARD  | .,    | Device current limit mode                                                                                 |

| 71        | VDRAIN_BREAKDOWN                                                                           |                  |       | 1700      | V     | Device breakdown voltage                                                                                  |

| 72        | DEVICE_GENERIC                                                                             |                  |       | INN39X9   |       | Device selection                                                                                          |

| 73        | DEVICE_CODE                                                                                | INN3949CQ        |       | INN3949CQ |       | Device code                                                                                               |

| 74        | PDEVICE_MAX                                                                                |                  |       | 70        | W     | Device maximum power capability                                                                           |

| 75        | RDSON_25DEG                                                                                |                  |       | 0.62      | Ω     | Primary switch on-time resistance at 25°C                                                                 |

| 76        | RDSON_125DEG                                                                               |                  |       | 1.10      | Ω     | Primary switch on-time resistance at 125°C                                                                |

| 77        | ILIMIT_MIN                                                                                 |                  |       | 1.767     | Α     | Primary switch minimum current limit                                                                      |

| 78        | ILIMIT_TYP                                                                                 |                  |       | 1.900     | Α     | Primary switch typical current limit                                                                      |

| 79        | ILIMIT_MAX                                                                                 |                  |       | 2.033     | Α     | Primary switch maximum current limit                                                                      |

| 80        | VDRAIN_ON_PRSW                                                                             |                  |       | 0.03      | V     | Primary switch on-time voltage drop                                                                       |

| 81        | VDRAIN_OFF_PRSW                                                                            |                  |       | 1230      | V     | Peak drain voltage on the primary switch during turn-off                                                  |

| 85        | WORST CASE ELECTRICA                                                                       | L PARAMETERS     | 5     |           | •     |                                                                                                           |

| 86        | FSWITCHING_MAX                                                                             | 33000            |       | 33000     | Hz    | Maximum switching frequency at full load and the valley of the minimum input AC voltage                   |

| 87        | VOR                                                                                        | 200.0            |       | 200.0     | V     | Voltage reflected to the primary winding (corresponding to set-point 1) when the primary switch turns off |

| 88        | KP                                                                                         |                  |       | 9.413     |       | Measure of continuous/discontinuous mode of operation                                                     |

| 89        | MODE_OPERATION                                                                             |                  |       | DCM       |       | Mode of operation                                                                                         |

| 90        | DUTYCYCLE                                                                                  |                  |       | 0.045     |       | Primary switch duty cycle                                                                                 |

| 91        | TIME_ON_MIN                                                                                |                  |       | 0.60      | us    | Minimum primary switch on-time                                                                            |

| 92        | TIME_ON_MAX                                                                                |                  |       | 1.56      | us    | Maximum primary switch on-time                                                                            |

| 93        | TIME_OFF                                                                                   |                  |       | 28.97     | us    | Primary switch off-time                                                                                   |

| 94        | LPRIMARY_MIN                                                                               |                  |       | 422.5     | uН    | Minimum primary magnetizing inductance                                                                    |

| 95        | LPRIMARY_TYP                                                                               |                  |       | 444.7     | uН    | Typical primary magnetizing inductance                                                                    |

| 96        | LPRIMARY_TOL                                                                               |                  |       | 5.0       | %     | Primary magnetizing inductance tolerance                                                                  |

| 97        | LPRIMARY_MAX                                                                               |                  |       | 467.0     | uH    | Maximum primary magnetizing inductance                                                                    |

| 99        | PRIMARY CURRENT                                                                            |                  |       |           | •     |                                                                                                           |

| 100       | IAVG_PRIMARY                                                                               |                  |       | 1.540     | Α     | Primary switch average current                                                                            |

| 101       | IPEAK_PRIMARY                                                                              |                  |       | 1.540     | A     | Primary switch peak current                                                                               |

| 102       | IPEDESTAL_PRIMARY                                                                          |                  |       | 0.031     | A     | Primary switch current pedestal                                                                           |

| 103       | IRIPPLE_PRIMARY                                                                            |                  |       | 1.540     | A     | Primary switch ripple current                                                                             |

| 104       | IRMS_PRIMARY                                                                               |                  |       | 0.180     | A     | Primary switch RMS current                                                                                |

| 108       | TRANSFORMER CONSTRU                                                                        | JCTION PARAM     | ETERS | 31100     | , ,,  | ,                                                                                                         |

| 109       | CORE SELECTION                                                                             | . J. LUIT AIVIII |       |           |       |                                                                                                           |

|           |                                                                                            |                  |       |           |       |                                                                                                           |

| 110 |                            | CUCTOM               | ı    | CUCTOM               |       | I a:                                                                      |

|-----|----------------------------|----------------------|------|----------------------|-------|---------------------------------------------------------------------------|

| 110 | CORE                       | CUSTOM               |      | CUSTOM               |       | Core selection                                                            |

| 111 | CORE NAME                  | EFD 25/13/9-<br>3C95 |      | EFD 25/13/9-<br>3C95 |       | Core code                                                                 |

| 112 | AE                         | 58.0                 |      | 58.0                 | mm^2  | Core cross sectional area                                                 |

| 113 | LE                         | 57.0                 |      | 57.0                 | mm    | Core magnetic path length                                                 |

| 114 | AL                         | 2660                 |      | 2660                 | nH    | Ungapped core effective inductance per turns squared                      |

| 115 | VE                         | 3300                 |      | 3300                 | mm^3  | Core volume                                                               |

|     |                            | MCT-EFD25-           |      | MCT-EFD25-N2         |       |                                                                           |

| 116 | BOBBIN NAME                | N2 H7+5P             |      | H7+5P                |       | Bobbin name                                                               |

| 117 | AW                         | 38.5                 |      | 38.5                 | mm^2  | Bobbin window area                                                        |

| 118 | BW                         | 16.20                |      | 16.20                | mm    | Bobbin width                                                              |

| 119 | MARGIN                     |                      |      | 0.0                  | mm    | Bobbin safety margin                                                      |

| 121 | PRIMARY WINDING            |                      | l    | 1 45                 |       | Diamento dia anno del conse                                               |

| 122 | NPRIMARY                   |                      |      | 45                   | Causa | Primary winding number of turns                                           |

| 123 | BPEAK                      |                      |      | 3723                 | Gauss | Peak flux density                                                         |

| 124 | BMAX                       |                      |      | 2689                 | Gauss | Maximum flux density                                                      |

| 125 | BAC                        |                      |      | 1344                 | Gauss | AC flux density (0.5 x Peak to Peak)                                      |

| 126 | ALG                        |                      |      | 220                  | nH    | Typical gapped core effective inductance per turns squared                |

| 127 | LG                         |                      |      | 0.304                | mm    | Core gap length                                                           |

| 129 | SECONDARY WINDING          |                      |      |                      |       |                                                                           |

| 130 | NSECONDARY                 |                      |      | 4                    |       | Secondary winding number of turns                                         |

| 132 | BIAS WINDING               |                      |      |                      |       |                                                                           |

| 133 | NBIAS                      |                      |      | 3                    |       | Bias winding number of turns                                              |

| 137 | PRIMARY COMPONENTS         | SELECTION            |      |                      |       |                                                                           |

| 138 | LINE UNDERVOLTAGE/O        | VERVOLTAGE           |      |                      |       |                                                                           |

| 139 | UVOV Type                  | UV Only              |      | UV Only              |       | Input Undervoltage/Overvoltage protection type                            |

| 140 | UNDERVOLTAGE<br>PARAMETERS |                      |      |                      |       |                                                                           |

| 141 | BROWN-IN REQUIRED          | 30.00                |      | 30.00                | V     | Required DC bus brown-in voltage threshold                                |

| 142 | UNDERVOLTAGE ZENER DIODE   | BZM55C9 V1           |      | BZM55C9 V1           |       | Undervoltage protection zener diode                                       |

| 143 | VZ                         |                      |      | 9.10                 | V     | Zener diode reverse voltage                                               |

| 144 | VR                         |                      |      | 6.80                 | V     | Zener diode reverse voltage at the maximum reverse leakage current        |

| 145 | ILKG                       |                      |      | 2.00                 | uA    | Zener diode maximum reverse leakage                                       |

| 146 | BROWN-IN ACTUAL            |                      |      | 22.99 - 29.55        | V     | Actual brown-in voltage range using                                       |

| 147 | PROWN OUT ACTUAL           |                      |      | 19.76 - 26.44        | V     | standard resistors Actual brown-out voltage range using                   |

| 14/ | BROWN-OUT ACTUAL           |                      |      | 13./0 - 20.44        | V     | standard resistors                                                        |

| 148 | OVERVOLTAGE<br>PARAMETERS  |                      |      |                      |       |                                                                           |

| 149 | OVERVOLTAGE REQUIRED       |                      | Info |                      | V     | For UV Only design, overvoltage feature is disabled                       |

| 150 | OVERVOLTAGE DIODE          |                      | Info |                      |       | OV diode is used only for the overvoltage protection circuit              |

| 151 | VF                         |                      |      |                      | V     | OV diode forward voltage                                                  |

| 152 | VRRM                       |                      |      |                      | V     | OV diode reverse voltage                                                  |

| 153 | PIV                        |                      |      |                      | V     | OV diode peak inverse voltage                                             |

| 154 | LINE_OVERVOLTAGE           |                      |      |                      | V     | For UV Only design, line overvoltage feature is disabled                  |

| 155 | DC BUS SENSE RESISTOR      | PS                   |      |                      |       | Tracture is disabled                                                      |

|     |                            |                      |      | 0.70                 | MO    | Connect five 140 kOhm DC bus upper                                        |

| 156 | RLS_H                      |                      |      | 0.70                 | ΜΩ    | sense resistors to the V-pin for the required UV/OV threshold             |

| 157 | RLS_L                      |                      |      | 261                  | kΩ    | DC bus lower sense resistor to the V-pin for the required UV/OV threshold |

| 160 | BIAS WINDING               |                      |      |                      |       |                                                                           |

| 161 | VBIAS                      |                      |      | 9.00                 | V     | Rectified bias voltage                                                    |

|     |                            |                      |      |                      |       |                                                                           |

| 162 | VE DIAC                    | 1.00         | 1.00                | 1/ | Disconinglish disde formed does                                            |

|-----|----------------------------|--------------|---------------------|----|----------------------------------------------------------------------------|

| 162 | VF_BIAS                    | 1.00         | 1.00                | V  | Bias winding diode forward drop                                            |

| 163 | VREVERSE_BIASDIODE         |              | 75.67               | V  | Bias diode reverse voltage (not accounting parasitic voltage ring)         |

| 164 | CBIAS                      |              | 22                  | uF | Bias winding rectification capacitor                                       |

| 165 | CBPP                       |              | 0.47                | uF | BPP pin capacitor                                                          |

| 169 | SECONDARY COMPONEN         | TS SELECTION |                     |    |                                                                            |

| 170 |                            |              |                     |    |                                                                            |

| 171 | RFB_UPPER                  |              | 100.00              | kΩ | Upper feedback resistor (connected to the output terminal)                 |

| 172 | RFB_LOWER                  |              | 7.50                | kΩ | Lower feedback resistor                                                    |

| 173 | CFB_LOWER                  |              | 330                 | pF | Lower feedback resistor decoupling capacitor                               |

| 177 | MULTIPLE OUTPUT PARAMETERS |              |                     |    |                                                                            |

| 178 | OUTPUT 1                   |              |                     |    |                                                                            |

| 179 | VOUT1                      |              | 18.00               | ٧  | Output 1 voltage                                                           |

| 180 | IOUT1                      | 0.555        | 0.555               | Α  | Output 1 current                                                           |

| 181 | POUT1                      |              | 9.99                | W  | Output 1 power                                                             |

| 182 | IRMS_SECONDARY1            |              | 2.330               | Α  | Root mean squared value of the secondary current for output 1              |

| 183 | IRIPPLE_CAP_OUTPUT1        |              | 2.263               | Α  | Current ripple on the secondary waveform for output 1                      |

| 184 | NSECONDARY1                |              | 4                   |    | Number of turns for output 1                                               |

| 185 | VREVERSE_RECTIFIER1        |              | 106.89              | V  | SRFET reverse voltage (not accounting parasitic voltage ring) for output 1 |

| 186 | SRFET1                     | AUTO         | DMT15H017LPS-<br>13 |    | Secondary rectifier (Logic MOSFET) for output 1                            |

| 187 | VF_SRFET1                  |              | 0.80                | V  | SRFET on-time drain voltage for output 1                                   |

| 188 | VBREAKDOWN_SRFET1          |              | 150                 | V  | SRFET breakdown voltage for output 1                                       |

| 189 | RDSON_SRFET1               |              | 26                  | mΩ | SRFET on-time drain resistance at 25degC and VGS=4.4V for output 1         |

| 191 | OUTPUT 2                   |              |                     |    |                                                                            |

| 192 | VOUT2                      | 9.00         | 9.00                | V  | Output 2 voltage                                                           |

| 193 | IOUT2                      | 0.333        | 0.333               | Α  | Output 2 current                                                           |

| 194 | POUT2                      |              | 3.00                | W  | Output 2 power                                                             |

| 195 | IRMS_SECONDARY2            |              | 1.398               | Α  | Root mean squared value of the secondary current for output 2              |

| 196 | IRIPPLE_CAP_OUTPUT2        |              | 1.358               | Α  | Current ripple on the secondary waveform for output 2                      |

| 197 | NSECONDARY2                |              | 2                   |    | Number of turns for output 2                                               |

| 198 | VREVERSE_RECTIFIER2        |              | 53.44               | V  | SRFET reverse voltage (not accounting parasitic voltage ring) for output 2 |

| 199 | SRFET2                     | AUTO         | SQSA80ENW           |    | Secondary rectifier (Logic MOSFET) for output 2                            |

| 200 | VF_SRFET2                  |              | 0.82                | ٧  | SRFET on-time drain voltage for output 2                                   |

| 201 | VBREAKDOWN_SRFET2          |              | 80                  | ٧  | SRFET breakdown voltage for output 2                                       |

| 202 | RDSON_SRFET2               |              | 27.0                | mΩ | SRFET on-time drain resistance at 25degC and VGS=4.4V for output 2         |

| 203 |                            |              |                     |    |                                                                            |

|     |                            |              |                     |    |                                                                            |

**Table 7** – DER-956Q PIXIs Spreadsheet.

## 9 **Performance Data**

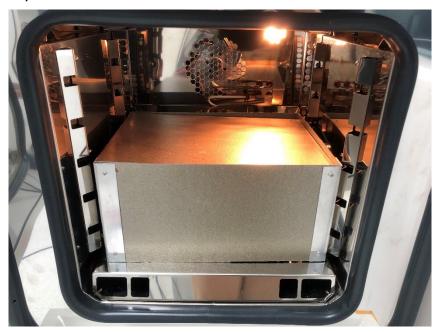

**Note:** 1. Measurements were taken with the unit under test set-up inside a thermal chamber placed inside a High Voltage (HV) room.

**Figure 12 –** High Voltage Test Set-up.

**Figure 13 -** Test Set-up Inside the High Voltage Room.

2. Unit under test was placed under a box while inside the thermal chamber to eliminate the effect of any airflow.

**Figure 14** – Unit under test placed under a box to eliminate the effect of airflow.

3. For data points showing performance across varying input line voltages and output loading conditions, the unit under test was soaked at full load condition for at least 5 minutes for every change in the input voltage during the start of each test sequence. Also, for every loading condition, the unit under test was soaked for at least 20 seconds before measurements were taken.

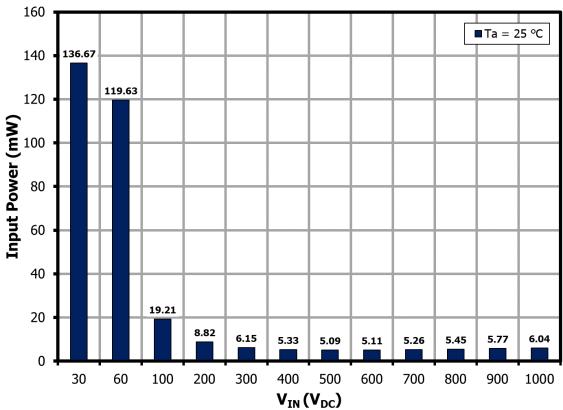

#### 9.1 No-Load Input Power

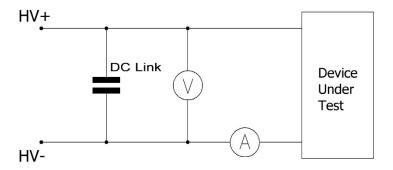

Figure 15 shows the test set up diagram for no load input current acquisition. The voltage metering point is placed before the ammeter; this is done to prevent the voltage sensing bias current from affecting the input current measurement. The ammeter used was Tektronix DMM 4050 6-1/2 Digit Precision Multimeter.

Figure 15 - No-Load Input Power Measurement Diagram.

The unit was soaked for ten minutes before starting data averaging of fifty thousand samples over a period of one minute. Analog filtering is also enabled to improve measurement accuracy.

Figure 16 - No-load Input Power vs. Input Line Voltage.

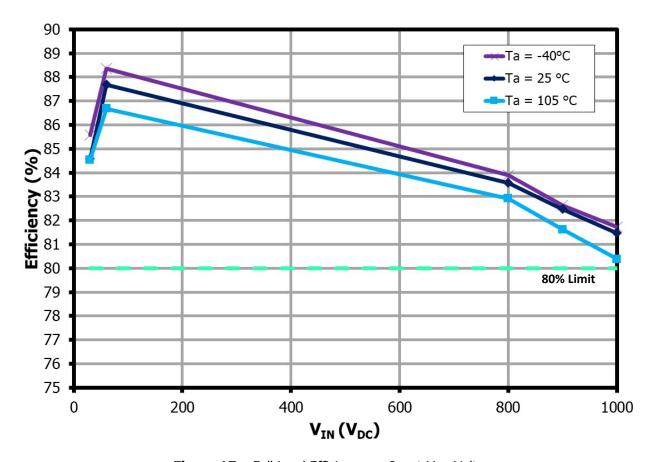

## 9.2 *Efficiency*

#### 9.2.1 Line Efficiency

Line efficiency describes how the change in input voltage affects the overall efficiency of the unit.

**Figure 17** – Full Load Efficiency vs. Input Line Voltage.

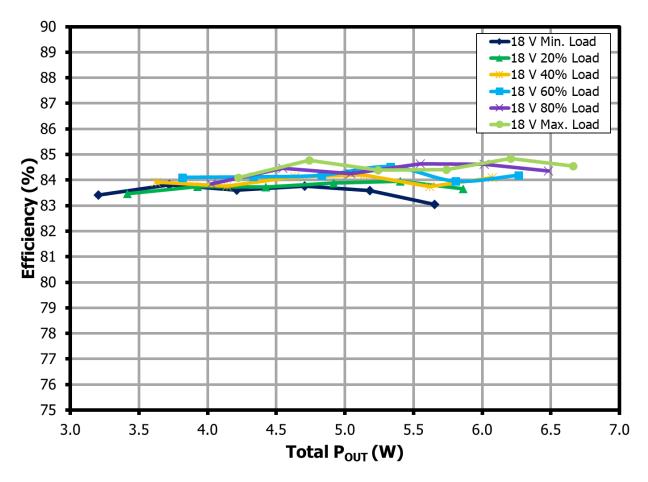

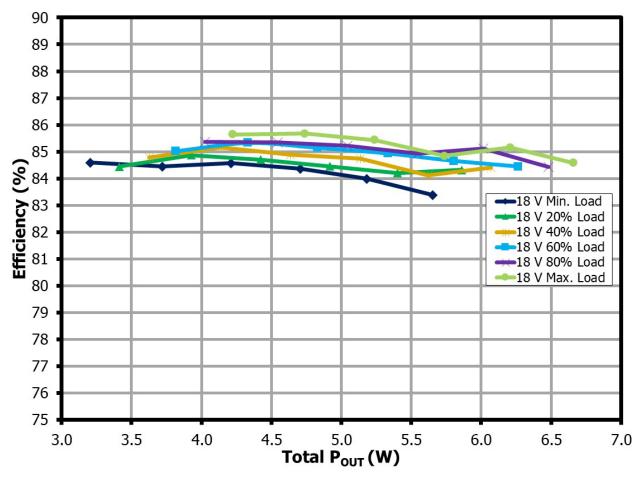

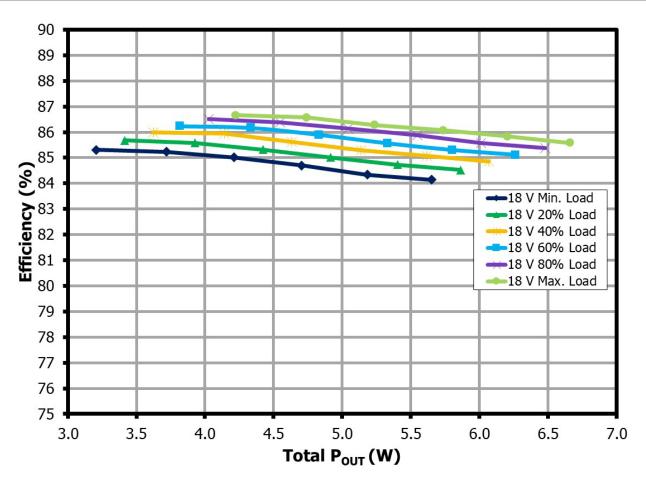

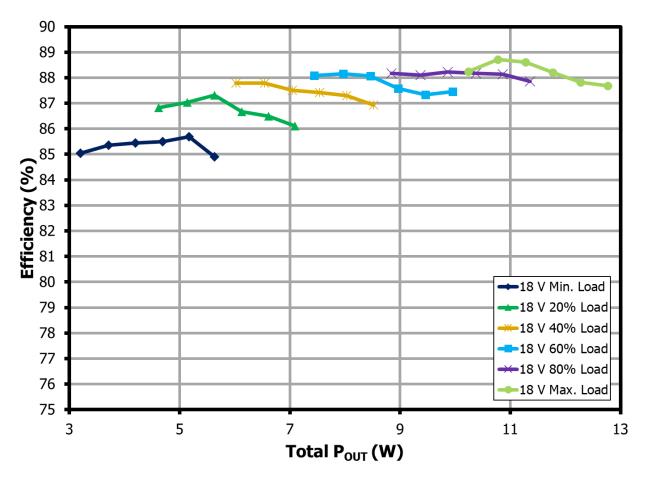

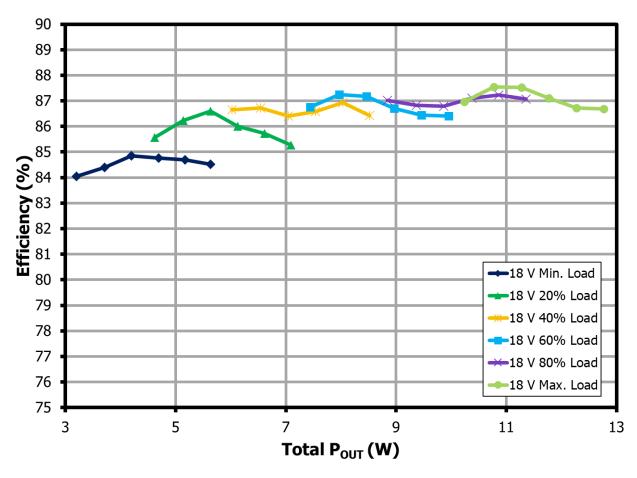

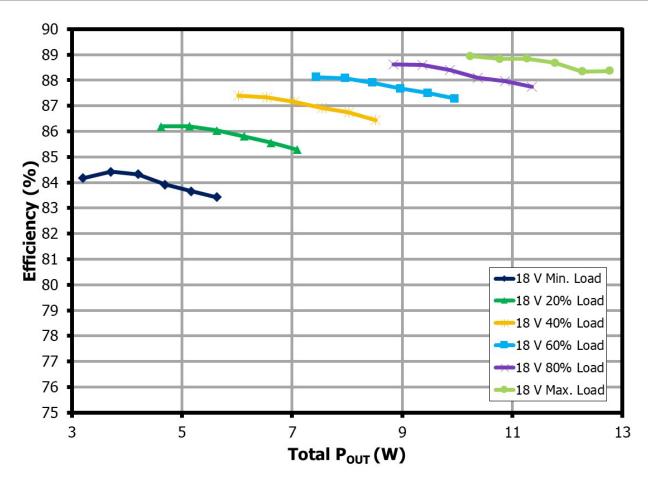

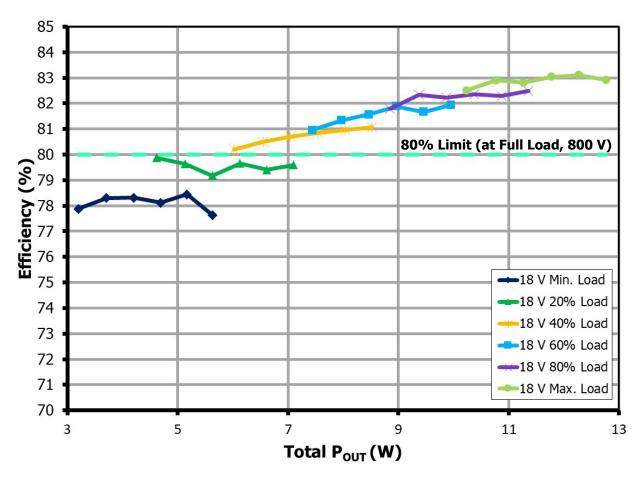

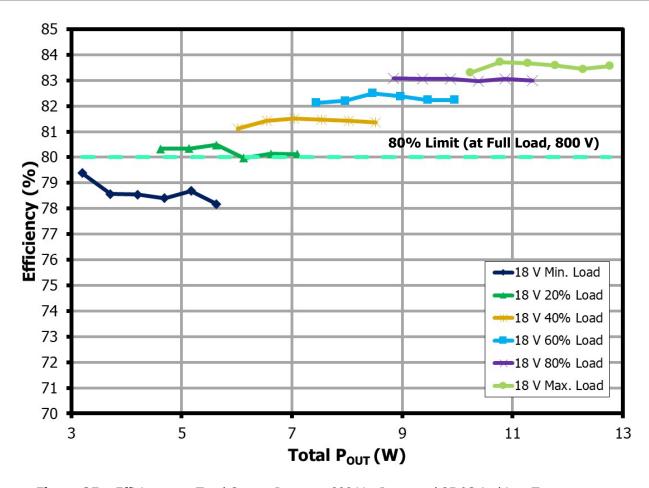

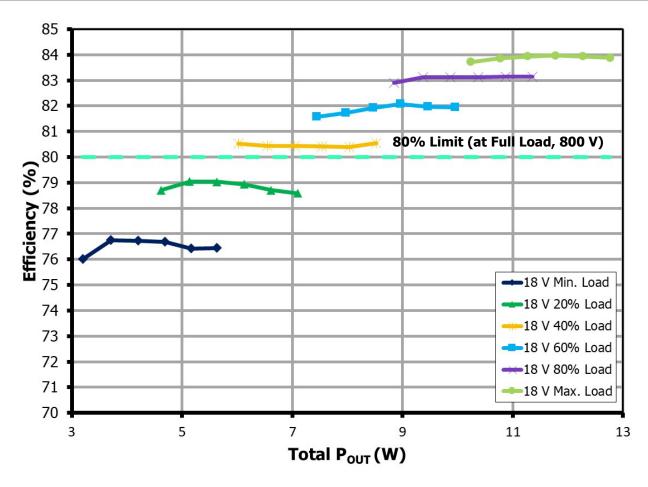

#### 9.2.2 Load Efficiency

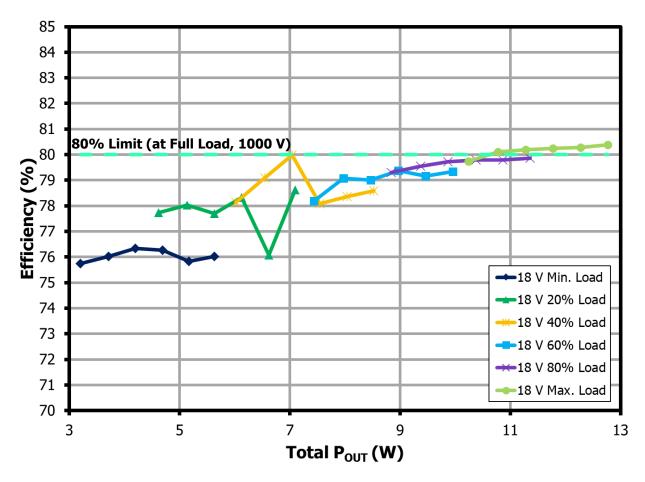

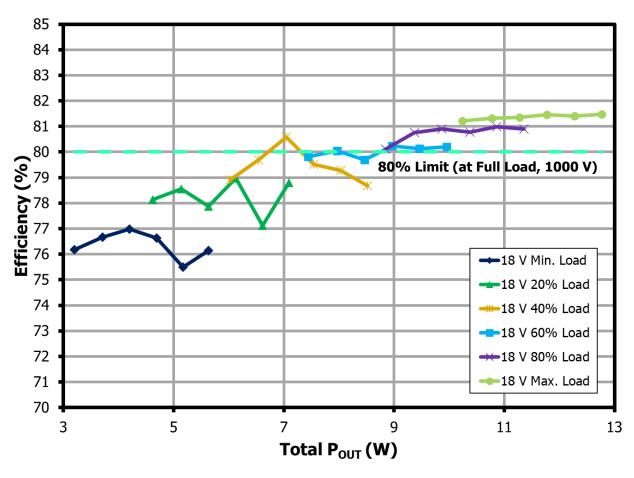

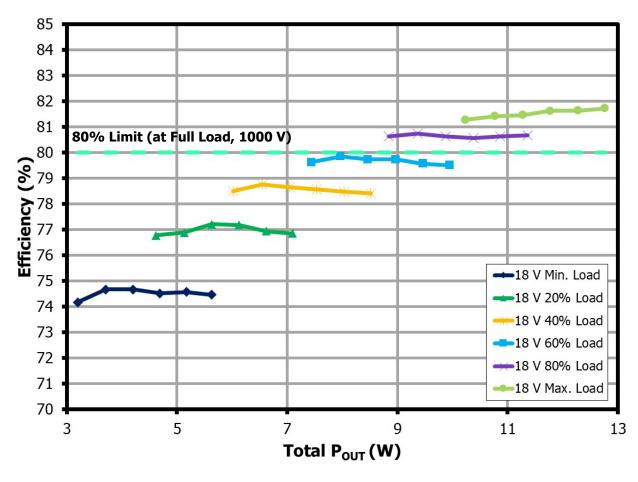

Load efficiency describes how the change in output loading conditions affects the overall efficiency of the unit.

Each line on the graphs represents the efficiency vs. total output power of the unit under test when the 18V output load is maintained at a certain percentage while the 9 V output load is increased from its minimum to maximum loading condition.

#### 9.2.2.1 30 V<sub>DC</sub> Input

**Figure 18** – Efficiency vs. Total Output Power at 30 V<sub>DC</sub> Input and 105 °C Ambient Temperature.

Figure 19 – Efficiency vs. Total Output Power at 30 V<sub>DC</sub> Input and 25 °C Ambient Temperature.

Figure 20 – Efficiency vs. Total Output Power at 30 V<sub>DC</sub> Input and -40 °C Ambient Temperature.

## 9.2.2.2 60 V<sub>DC</sub> Input

**Figure 21** – Efficiency vs. Total Output Power at 60 V<sub>DC</sub> Input and 105 °C Ambient Temperature.

**Figure 22** – Efficiency vs. Total Output Power at 60 V<sub>DC</sub> Input and 25 °C Ambient Temperature.

Figure 23 – Efficiency vs. Total Output Power at 60 VDC Input and -40 °C Ambient Temperature.

# 9.2.2.3 800 V<sub>DC</sub> Input

Figure 24 – Efficiency vs. Total Output Power at 800 V<sub>DC</sub> Input and 105 °C Ambient Temperature.

Figure 25 – Efficiency vs. Total Output Power at 800 V<sub>DC</sub> Input and 25 °C Ambient Temperature.

Figure 26 – Efficiency vs. Total Output Power at 800 V<sub>DC</sub> Input and -40 °C Ambient Temperature.

## 9.2.2.4 1000 V<sub>DC</sub> Input

**Figure 27** − Efficiency vs. Total Output Power at 1000 V<sub>DC</sub> Input and 105 °C Ambient Temperature.

**Figure 28** – Efficiency vs. Total Output Power at 1000 V<sub>DC</sub> Input and 25 °C Ambient Temperature.

Figure 29 − Efficiency vs. Total Output Power at 1000 V<sub>DC</sub> Input and -40 °C Ambient Temperature.

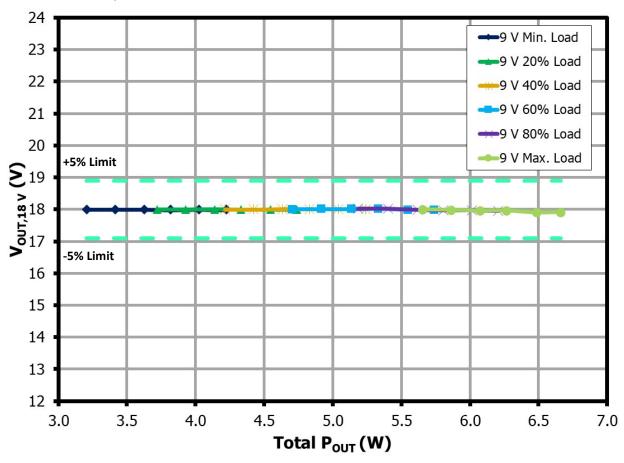

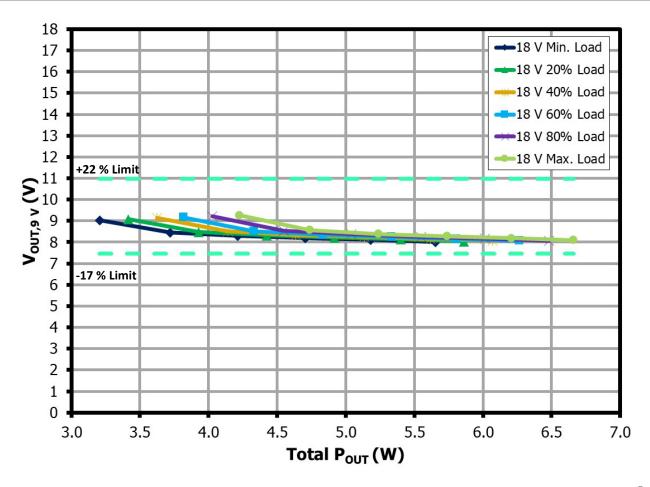

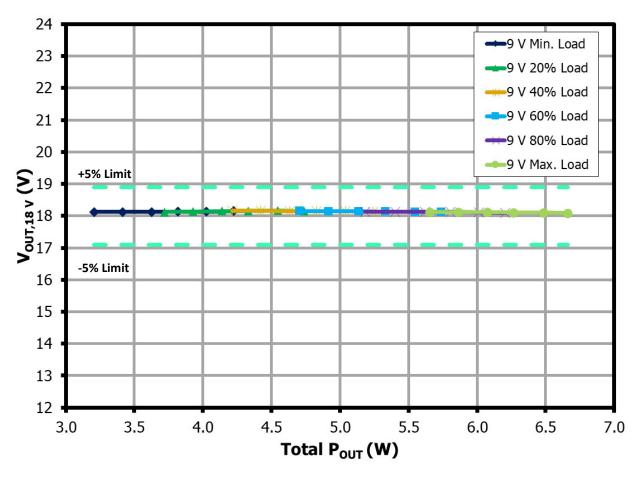

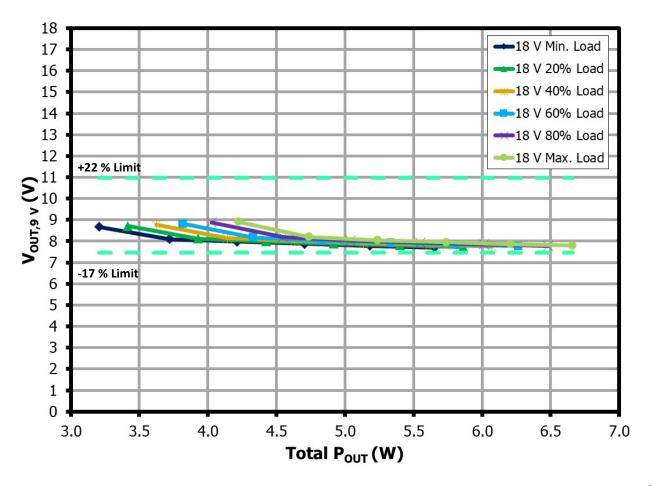

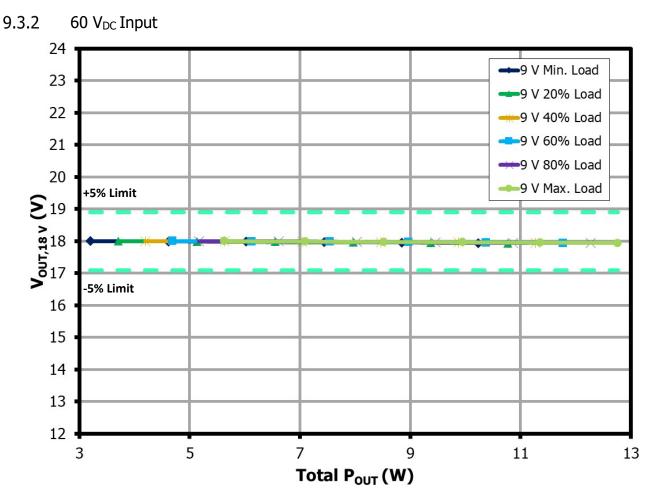

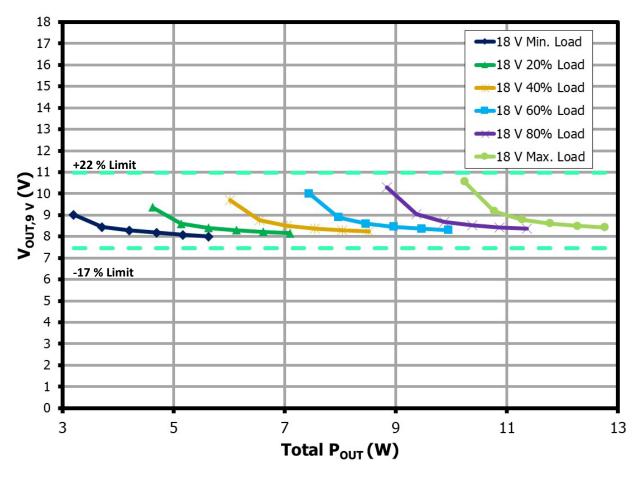

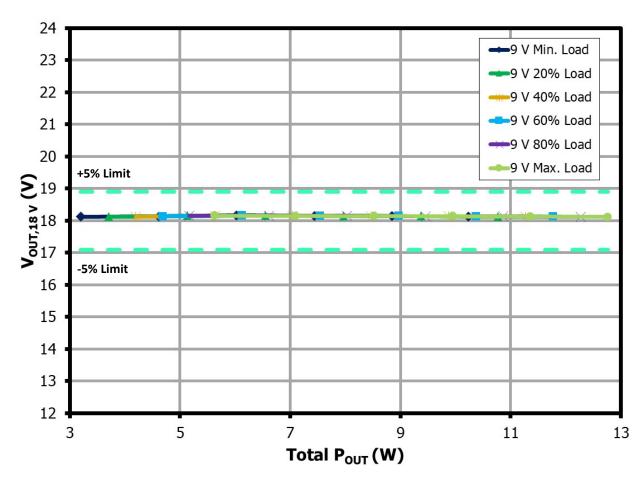

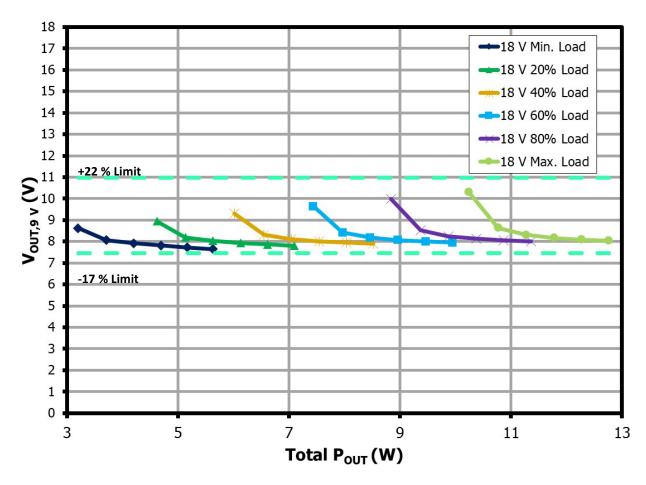

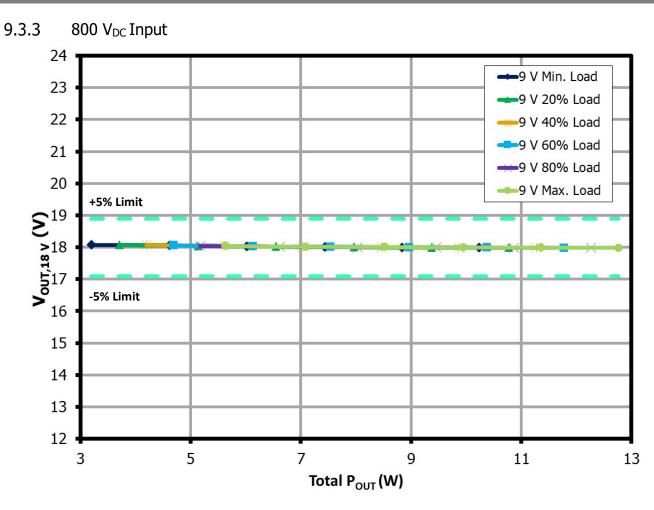

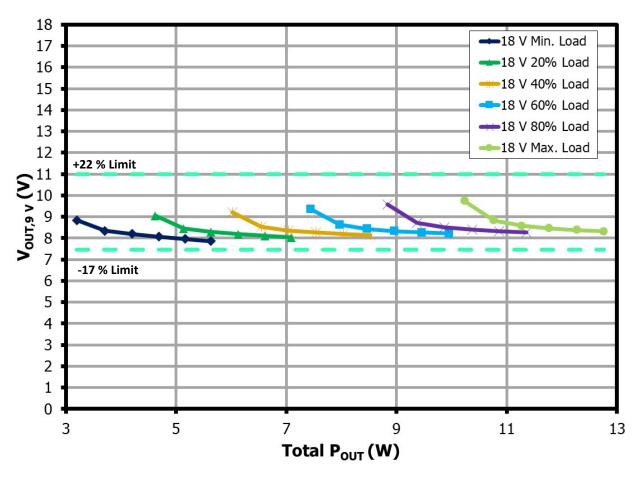

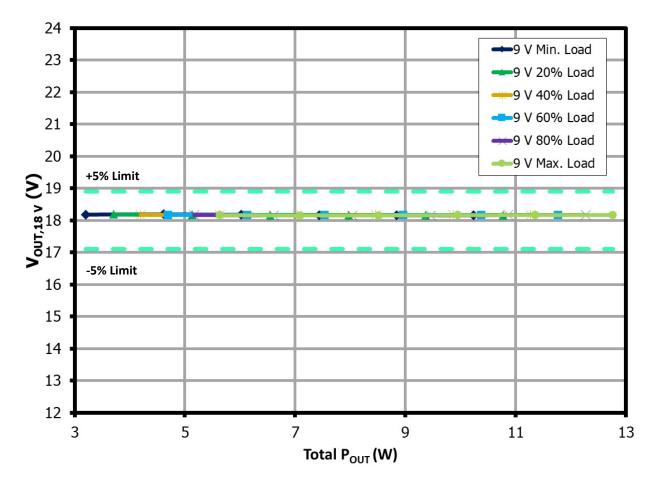

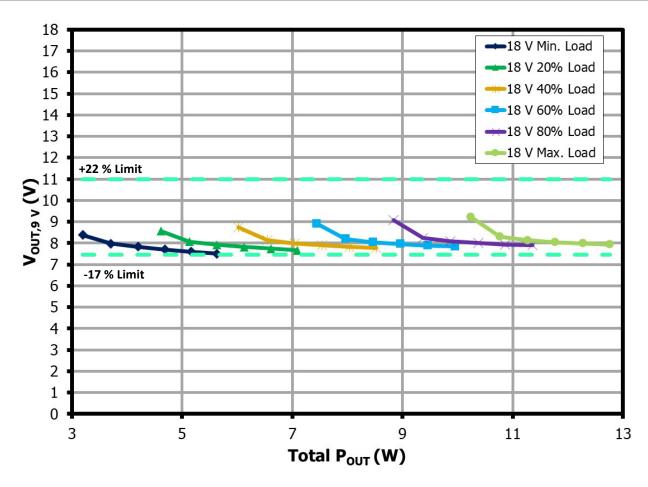

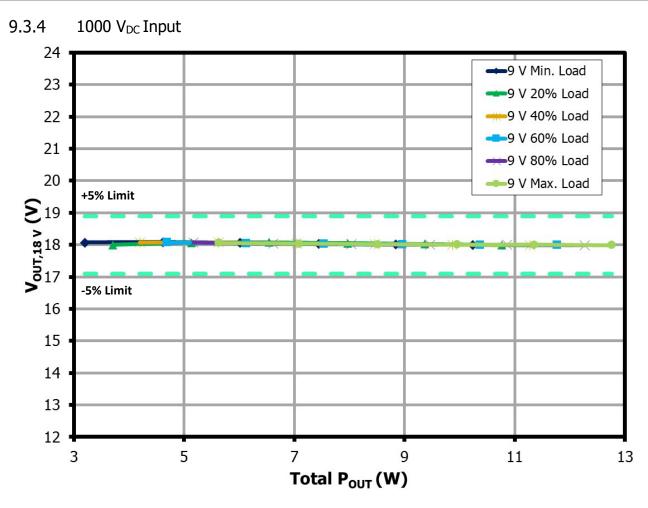

#### 9.3 Load Regulation

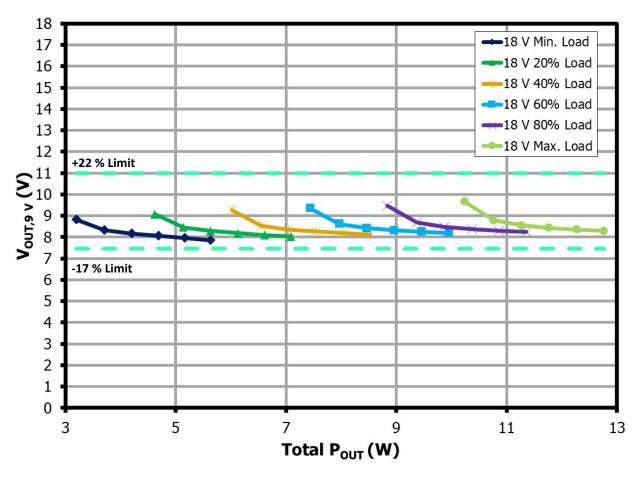

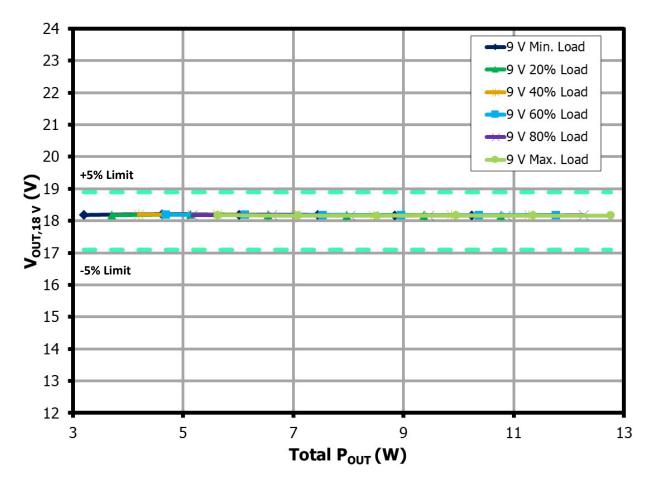

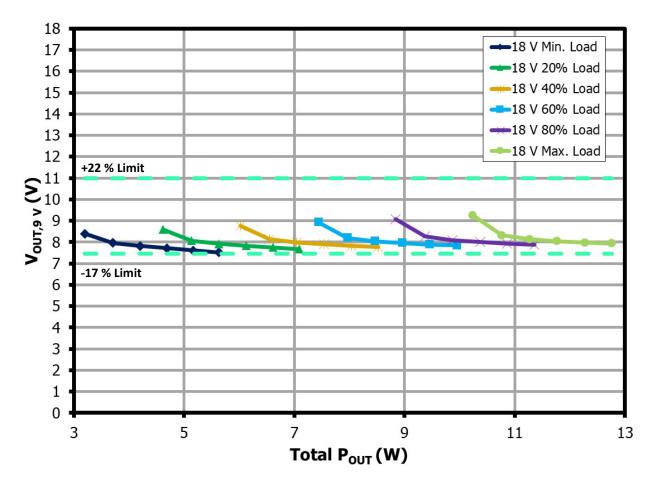

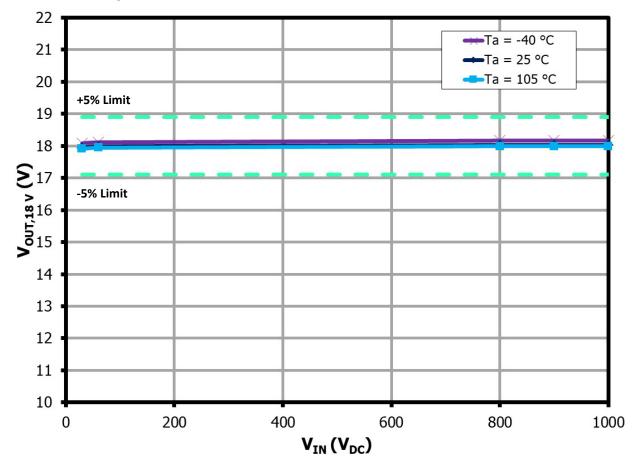

Load regulation describes how loading conditions (minimum – maximum) affect the output voltage of the unit.

#### 9.3.1 30 V<sub>DC</sub> Input

**Figure 30** - 18 V Output Voltage vs. Total Output Power at 30  $V_{DC}$  Input and 105  $^{\circ}C$  Ambient Temperature.  $^{6}$

<sup>&</sup>lt;sup>6</sup> Each line represents the 18 V output regulation vs. total output power of the unit under test when the 9 V output load is maintained at a certain percentage while the 18 V output load is increased from its minimum to maximum loading condition.

Figure 31 – 9 V Output Voltage vs. Total Output Power at 30 V<sub>DC</sub> Input and 105 °C Ambient Temperature.<sup>7</sup>

<sup>&</sup>lt;sup>7</sup> Each line represents the 9 V output regulation vs. total output power of the unit under test when the 18 V output load is maintained at a certain percentage while the 9 V output load is increased from its minimum to maximum loading condition.

Figure 32 - 18 V Output Voltage vs. Total Output Power at 30 V<sub>DC</sub> Input and -40 °C Ambient Temperature.<sup>8</sup>

<sup>&</sup>lt;sup>8</sup> Each line represents the 18 V output regulation vs. total output power of the unit under test when the 9 V output load is maintained at a certain percentage while the 18 V output load is increased from its minimum to maximum loading condition.

Figure 33 – 9 V Output Voltage vs. Total Output Power at 30 V<sub>DC</sub> Input and -40 °C Ambient Temperature.<sup>9</sup>

<sup>&</sup>lt;sup>9</sup> Each line represents the 9 V output regulation vs. total output power of the unit under test when the 18 V output load is maintained at a certain percentage while the 9 V output load is increased from its minimum to maximum loading condition.

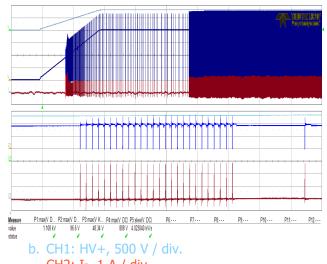

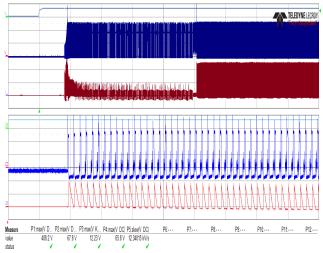

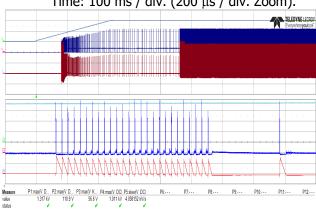

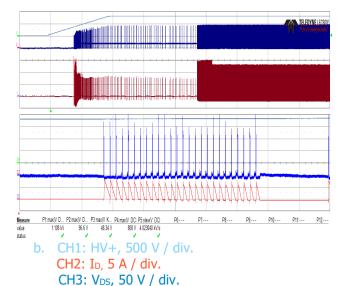

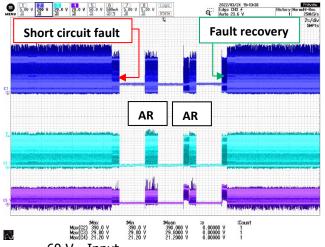

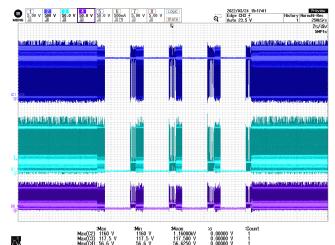

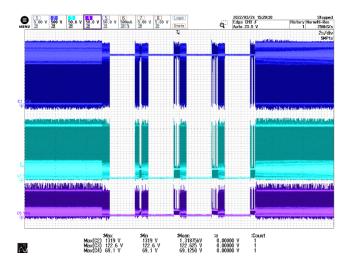

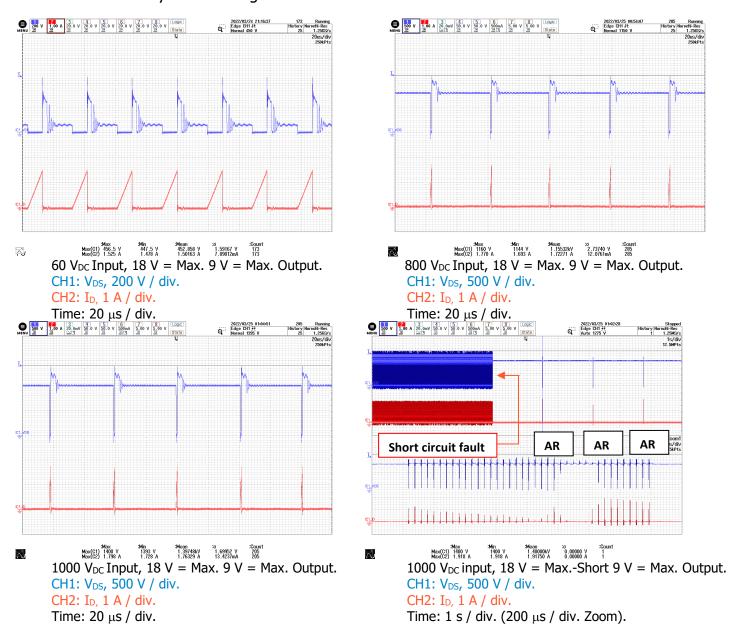

Figure 34 – 18 V Output Voltage vs. Total Output Power at 60 V<sub>DC</sub> Input and 105 °C Ambient Temperature. 10